MITIGATING THE EFFECT OF MISSPECULATIONS IN SUPERSCALAR

PROCESSORS

By

Zhaoxiang Jin

A DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

In Computer Science

MICHIGAN TECHNOLOGICAL UNIVERSITY

2018

This dissertation has been approved in partial fulfillment of the requirements for the

Degree of DOCTOR OF PHILOSOPHY in Computer Science.

Department of Computer Science

Dissertation Advisor: *Dr. Soner Onder*

Committee Member: *Dr. Zhenlin Wang #1*

Committee Member: *Dr. Saeid Nooshabadi #2*

Committee Member: *Dr. David Whalley #3*

Department Chair: *Dr. Min Song*

## **Dedication**

To my parents: Jin, Jianmin (Dad) and Xu, Huizhu (Mom)

You always encourage me to pursue my dreams and provide me everything I need.

Without your inspiration and help, there was no way for me to get this far.

To my advisor: Önder, Soner

Who didn't hesitate to criticize my work at every stage - without which I would neither be who I am nor would this work be what it is today.

To my friends

Thank you for being my friends and never giving up on me. I have learned a lot things which you can never learn from any book in this world, from all of you. Without you, it's impossible for me to come with these innovative ideas.

# Contents

|                                                |              |

|------------------------------------------------|--------------|

| <b>List of Figures</b> . . . . .               | <b>xv</b>    |

| <b>List of Tables</b> . . . . .                | <b>xix</b>   |

| <b>Author Contribution Statement</b> . . . . . | <b>xxi</b>   |

| <b>List of Abbreviations</b> . . . . .         | <b>xxiii</b> |

| <b>Abstract</b> . . . . .                      | <b>xxv</b>   |

| <b>1 Introduction</b> . . . . .                | <b>1</b>     |

| 1.1 A Superscalar Processor . . . . .          | 5            |

| 1.1.1 The Front-end . . . . .                  | 5            |

| 1.1.2 The Back-end . . . . .                   | 6            |

| 1.1.3 Register Alias Table . . . . .           | 7            |

| 1.2 Speculative Execution . . . . .            | 8            |

| 1.2.1 Branch Prediction . . . . .              | 8            |

| 1.2.2 Memory Ordering Prediction . . . . .     | 11           |

| 1.3 Misspeculation Recovery . . . . .          | 14           |

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| 1.3.1    | Recovering Branch Predictor State . . . . .                      | 16        |

| 1.3.2    | Restoring the Map Tables . . . . .                               | 18        |

| 1.3.3    | Eliminating Stale Instructions . . . . .                         | 19        |

| 1.4      | Recovery Penalty Analysis . . . . .                              | 19        |

| 1.4.1    | Misspeculation Detection Delay . . . . .                         | 20        |

| 1.4.2    | Stale Instruction Elimination Delay . . . . .                    | 21        |

| 1.4.3    | State Restoration Delay . . . . .                                | 21        |

| 1.4.4    | Pipeline Fill Delay . . . . .                                    | 22        |

| 1.5      | Summary . . . . .                                                | 23        |

| <b>2</b> | <b>Mower : A Walking-based Misspeculation Recovery Mechanism</b> | <b>25</b> |

| 2.1      | Overview . . . . .                                               | 25        |

| 2.1.1    | Recovering F-RAT by Walking . . . . .                            | 26        |

| 2.1.2    | Checkpointing Architectures . . . . .                            | 29        |

| 2.1.3    | Motivation . . . . .                                             | 31        |

| 2.2      | Control Dependence Tracking . . . . .                            | 35        |

| 2.2.1    | Branch Renaming . . . . .                                        | 35        |

| 2.2.2    | Disambiguating the Branch Ordering . . . . .                     | 36        |

| 2.2.3    | Tracking Affected F-RAT entries . . . . .                        | 38        |

| 2.3      | A Reverse Walking Procedure . . . . .                            | 39        |

| 2.3.1    | Recovering F-RAT in a gradual manner . . . . .                   | 39        |

| 2.3.2    | Eliminating Stale Instructions . . . . .                         | 40        |

|          |                                                             |           |

|----------|-------------------------------------------------------------|-----------|

| 2.4      | Microarchitecture . . . . .                                 | 42        |

| 2.4.1    | Branch Tag Allocation and Release . . . . .                 | 43        |

| 2.4.2    | Branch and Mapping Dependence Matrices . . . . .            | 44        |

| 2.4.3    | Reclaiming the Resources using a single Read Port . . . . . | 46        |

| 2.5      | Evaluation . . . . .                                        | 47        |

| 2.5.1    | Evaluation Methodology . . . . .                            | 48        |

| 2.5.2    | Branch Tag Size Effect . . . . .                            | 51        |

| 2.5.3    | Invalid Register Mappings . . . . .                         | 52        |

| 2.5.4    | Eliminating Invalid Instructions . . . . .                  | 53        |

| 2.5.5    | The Front-end and Back-end depth . . . . .                  | 54        |

| 2.5.6    | Energy Efficiency . . . . .                                 | 55        |

| 2.6      | Summary . . . . .                                           | 58        |

| <b>3</b> | <b>Two-Phase Misspeculation Recovery . . . . .</b>          | <b>61</b> |

| 3.1      | Overview . . . . .                                          | 61        |

| 3.1.1    | A Basic Recovery Mechanism . . . . .                        | 62        |

| 3.1.2    | Analysis and Related Work . . . . .                         | 64        |

| 3.1.3    | Key Observation . . . . .                                   | 67        |

| 3.2      | Preliminary Analysis . . . . .                              | 70        |

| 3.3      | Microarchitecture . . . . .                                 | 73        |

| 3.3.1    | Initialization . . . . .                                    | 73        |

| 3.3.2    | Three Different Flushing Policies . . . . .                 | 75        |

|          |                                                                  |           |

|----------|------------------------------------------------------------------|-----------|

| 3.3.3    | Fetch Policy . . . . .                                           | 76        |

| 3.3.4    | F-RAT and Free Register Pool . . . . .                           | 77        |

| 3.3.5    | Speculative Recovery . . . . .                                   | 77        |

| 3.3.6    | Complexity Comparison . . . . .                                  | 78        |

| 3.4      | Evaluation . . . . .                                             | 80        |

| 3.4.1    | Simulation Methodology . . . . .                                 | 80        |

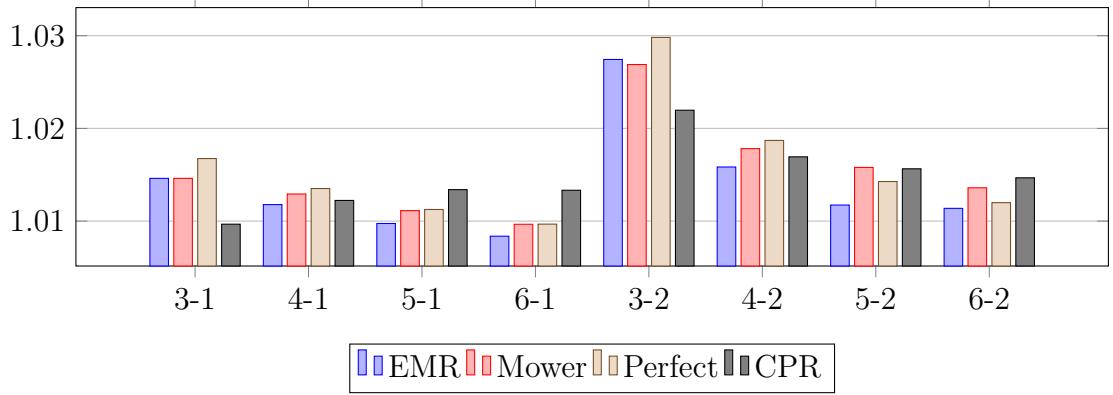

| 3.4.2    | Recover Afterwards and Two-Phase . . . . .                       | 85        |

| 3.4.3    | Recover Beforehand and Two-Phase . . . . .                       | 87        |

| 3.4.4    | Allocation Algorithms in Checkpointing Architectures . . . . .   | 89        |

| 3.4.5    | Memory Latency Effect . . . . .                                  | 90        |

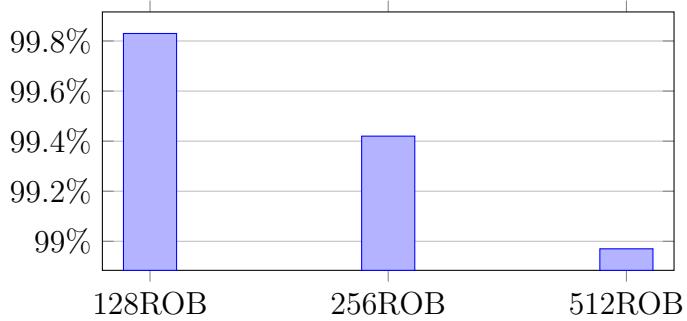

| 3.4.6    | ROB Size Effect . . . . .                                        | 91        |

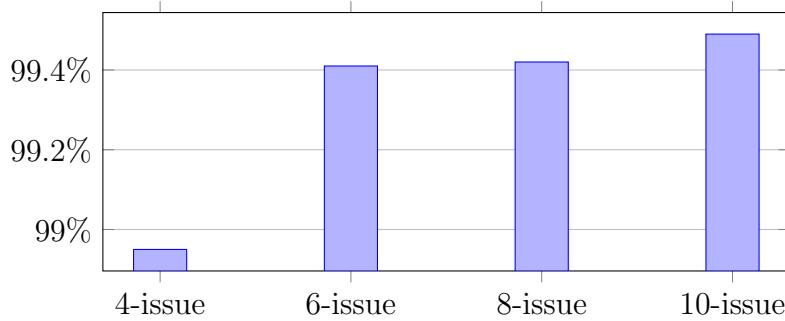

| 3.4.7    | Issue Width Effect . . . . .                                     | 92        |

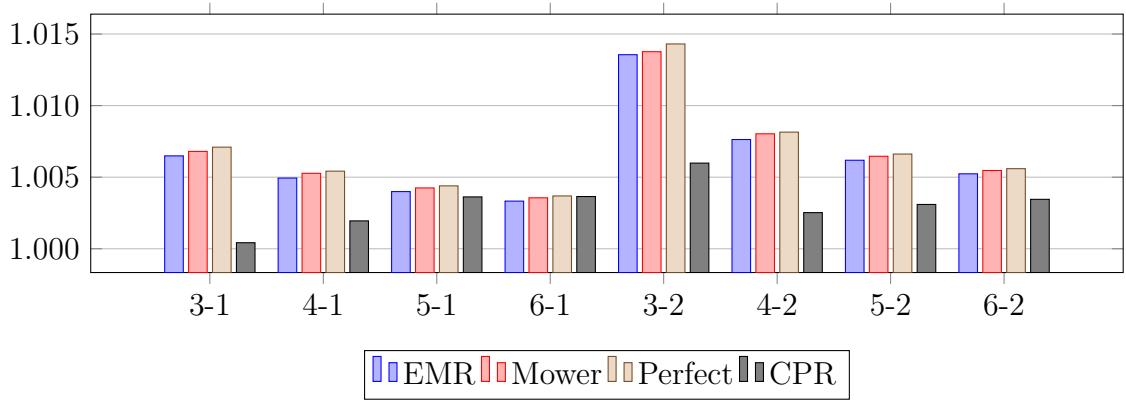

| 3.4.8    | Power Efficiency . . . . .                                       | 92        |

| 3.5      | Summary . . . . .                                                | 93        |

| <b>4</b> | <b>Passing Loop : Reducing the Pipeline Fill Delay . . . . .</b> | <b>95</b> |

| 4.1      | Overview . . . . .                                               | 95        |

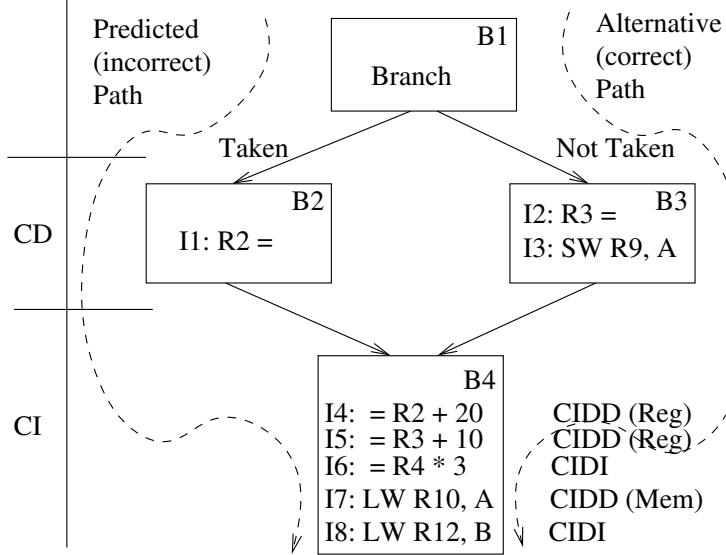

| 4.1.1    | Control Independence . . . . .                                   | 96        |

| 4.1.2    | The Convergence Point Prediction . . . . .                       | 97        |

| 4.1.3    | The Affected Register Mapping . . . . .                          | 98        |

| 4.1.4    | Correct Instruction Insertion . . . . .                          | 99        |

| 4.2      | Related Work . . . . .                                           | 99        |

|          |                                                        |            |

|----------|--------------------------------------------------------|------------|

| 4.2.1    | Eager Execution . . . . .                              | 100        |

| 4.2.2    | Control Independence . . . . .                         | 104        |

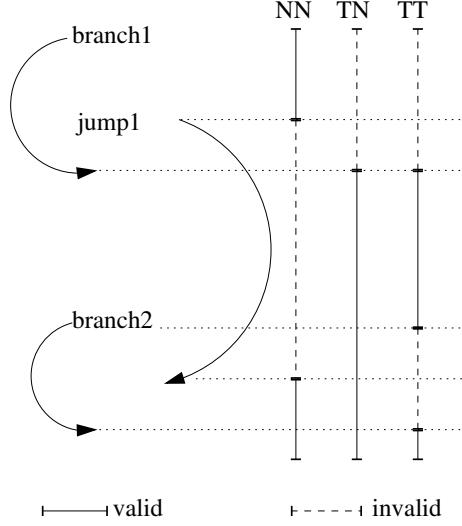

| 4.3      | The Concept of Passing Loop . . . . .                  | 106        |

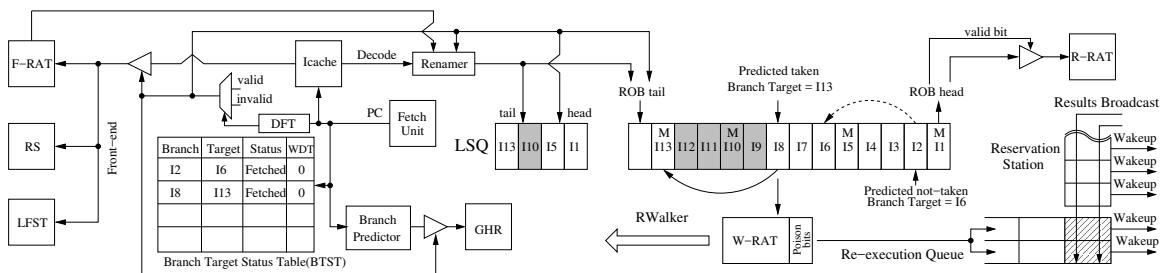

| 4.4      | Microarchitecture . . . . .                            | 110        |

| 4.4.1    | Front-end: Fetching Algorithm . . . . .                | 112        |

| 4.4.2    | Handling Memory Instructions . . . . .                 | 115        |

| 4.4.3    | Back-end: Misprediction Recovery . . . . .             | 116        |

| 4.4.4    | CIDD redundancy . . . . .                              | 120        |

| 4.5      | Experimental Results . . . . .                         | 121        |

| 4.5.1    | Simulation Methodology . . . . .                       | 121        |

| 4.5.2    | Performance Analysis . . . . .                         | 124        |

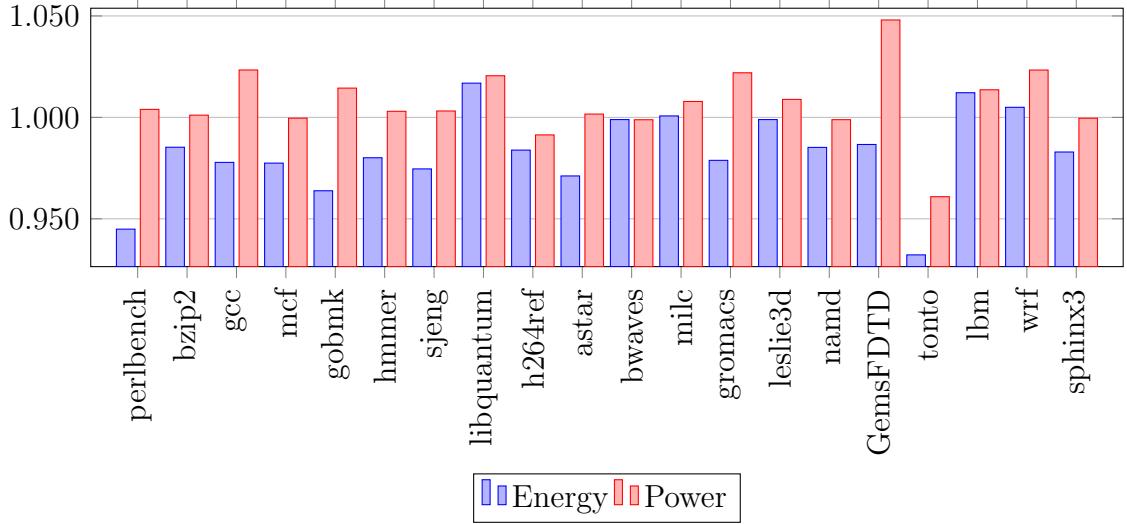

| 4.5.3    | Energy Efficiency . . . . .                            | 132        |

| 4.5.4    | Design Complexity . . . . .                            | 134        |

| 4.6      | Summary . . . . .                                      | 135        |

| <b>5</b> | <b>Dynamic Memory Dependence Predication . . . . .</b> | <b>137</b> |

| 5.1      | Overview . . . . .                                     | 138        |

| 5.2      | Motivation . . . . .                                   | 140        |

| 5.3      | The Concept of Memory Predication . . . . .            | 144        |

| 5.4      | Microarchitecture . . . . .                            | 148        |

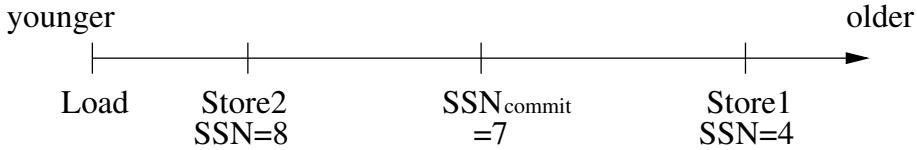

| 5.4.1    | Store Vulnerability Window . . . . .                   | 149        |

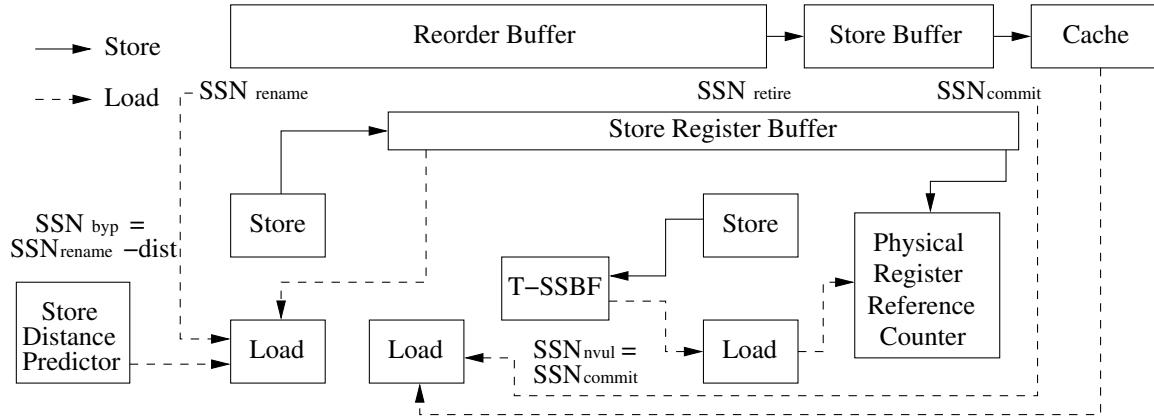

| 5.4.2    | Tagged Store Sequence Bloom Filter . . . . .           | 150        |

|        |                                               |     |

|--------|-----------------------------------------------|-----|

| 5.4.3  | Load Re-execution . . . . .                   | 151 |

| 5.4.4  | Memory Dependence Prediction . . . . .        | 152 |

| 5.4.5  | Memory Cloaking . . . . .                     | 153 |

| 5.4.6  | Predication Insertion . . . . .               | 155 |

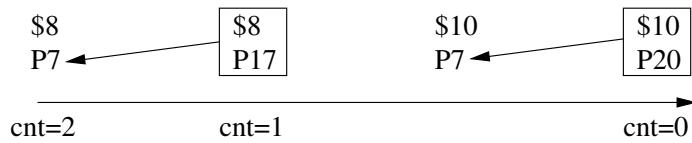

| 5.4.7  | Physical Register Reference Counter . . . . . | 157 |

| 5.4.8  | Load Re-execution Filter . . . . .            | 159 |

| 5.4.9  | Silent Store Effect . . . . .                 | 160 |

| 5.4.10 | Partial-Word Forwarding . . . . .             | 161 |

| 5.4.11 | Confidence Predictor . . . . .                | 163 |

| 5.4.12 | Memory Consistency . . . . .                  | 164 |

| 5.5    | Evaluation Methodology . . . . .              | 165 |

| 5.6    | Experimental Results . . . . .                | 169 |

| 5.6.1  | NoSQ VS. Baseline . . . . .                   | 169 |

| 5.6.2  | DMDP VS. Baseline . . . . .                   | 171 |

| 5.6.3  | DMDP VS. NoSQ . . . . .                       | 172 |

| 5.6.4  | DMDP VS. Perfect . . . . .                    | 173 |

| 5.6.5  | Case Study in <i>bzip2</i> . . . . .          | 176 |

| 5.6.6  | Store Buffer Size Effect . . . . .            | 177 |

| 5.6.7  | Alternative Configurations . . . . .          | 178 |

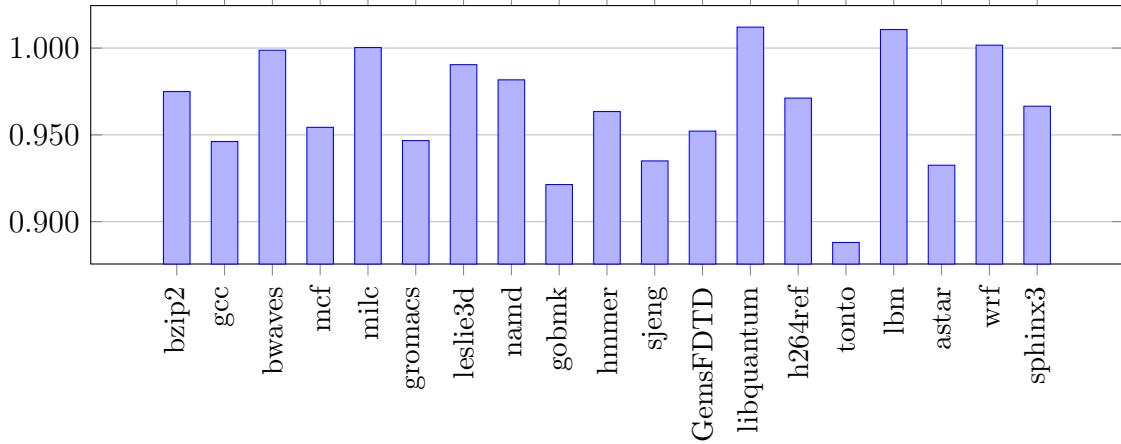

| 5.6.8  | Energy Efficiency . . . . .                   | 179 |

| 5.7    | Related Work . . . . .                        | 180 |

|                                         |            |

|-----------------------------------------|------------|

| 5.8 Summary . . . . .                   | 183        |

| <b>6 Conclusion . . . . .</b>           | <b>185</b> |

| <b>References . . . . .</b>             | <b>189</b> |

| <b>A Copyright Permission . . . . .</b> | <b>205</b> |

# List of Figures

|      |                                                                  |    |

|------|------------------------------------------------------------------|----|

| 1.1  | The block diagram of a superscalar processor . . . . .           | 5  |

| 1.2  | From logical register space to physical register space . . . . . | 7  |

| 1.3  | Gshare branch predictor . . . . .                                | 9  |

| 1.4  | Branch Target Buffer . . . . .                                   | 10 |

| 1.5  | Return Address Stack . . . . .                                   | 10 |

| 1.6  | Store Queue . . . . .                                            | 12 |

| 1.7  | Load Queue . . . . .                                             | 13 |

| 1.8  | Store Set mechanism . . . . .                                    | 14 |

| 1.9  | Branch misprediction recovery . . . . .                          | 15 |

| 1.10 | Recover Branch History Register . . . . .                        | 17 |

| 1.11 | Recover Register Alias Table . . . . .                           | 19 |

| 2.1  | Restoring the mapping table by history buffer . . . . .          | 27 |

| 2.2  | Renaming with a not fully correct F-RAT . . . . .                | 33 |

| 2.3  | The different walking direction in Mower . . . . .               | 34 |

| 2.4  | The branch dependence matrix . . . . .                           | 37 |

| 2.5  | The mapping dependence matrix . . . . .                          | 38 |

|      |                                                                                                            |    |

|------|------------------------------------------------------------------------------------------------------------|----|

| 2.6  | Recovering F-RAT by walking from the misprediction to ROB tail . . . . .                                   | 40 |

| 2.7  | Reclaiming the back-end resources via the walking process . . . . .                                        | 42 |

| 2.8  | The block diagram of Mower . . . . .                                                                       | 43 |

| 2.9  | Branch Dependence Register, tracking all of the unresolved branches                                        | 44 |

| 2.10 | Branch Dependence Register collaborates with Branch Dependence Matrix . . . . .                            | 45 |

| 2.11 | Sharing of one access port by the walker and the ROB tail . . . . .                                        | 47 |

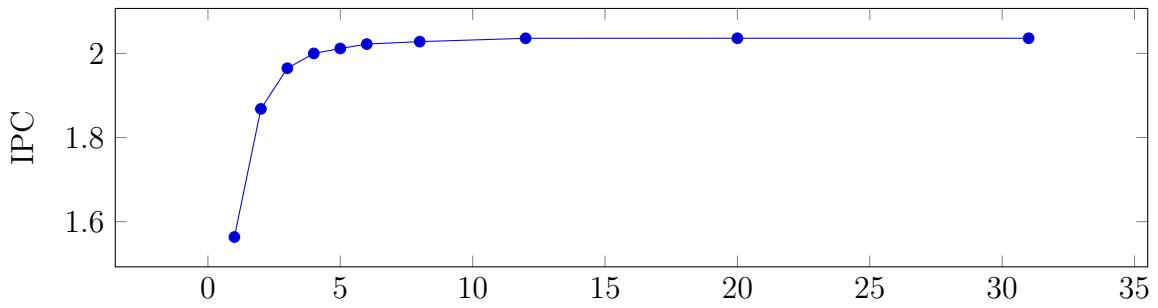

| 2.12 | IPC vs number of unresolved branches . . . . .                                                             | 51 |

| 2.13 | The number of invalid register mappings through the walking process                                        | 52 |

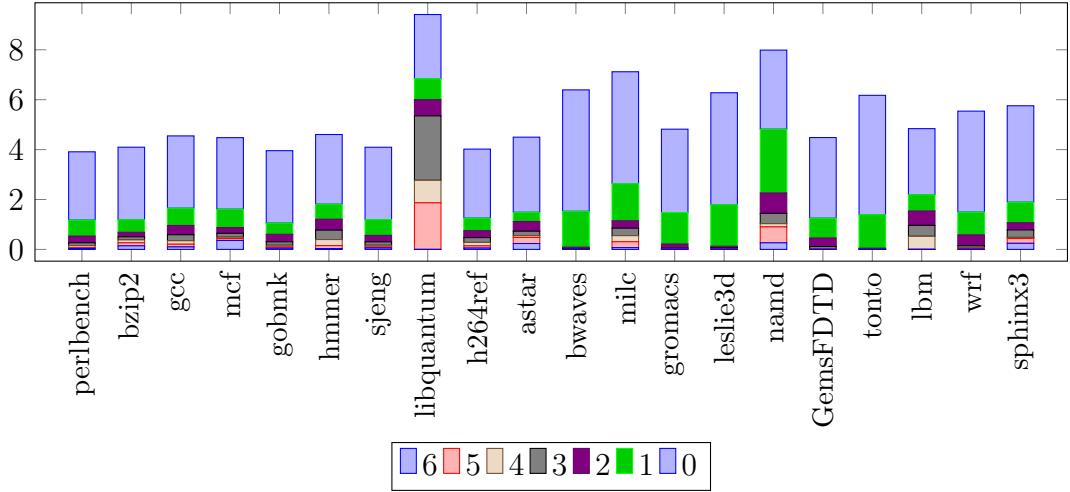

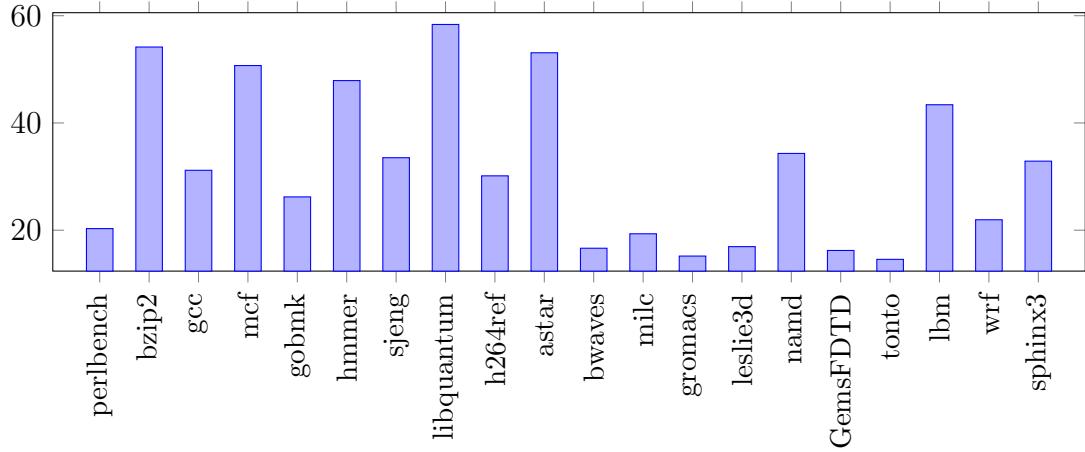

| 2.14 | The average number of invalid instructions left in the pipeline when a misprediction is detected . . . . . | 53 |

| 2.15 | Spec2006 Integer Speedup (Normalized to Baseline) . . . . .                                                | 55 |

| 2.16 | Spec2006 Float Speedup (Normalized to Baseline) . . . . .                                                  | 55 |

| 2.17 | Power Evaluation (Normalized to Baseline) . . . . .                                                        | 56 |

| 2.18 | EDP normalized to the baseline configuration . . . . .                                                     | 58 |

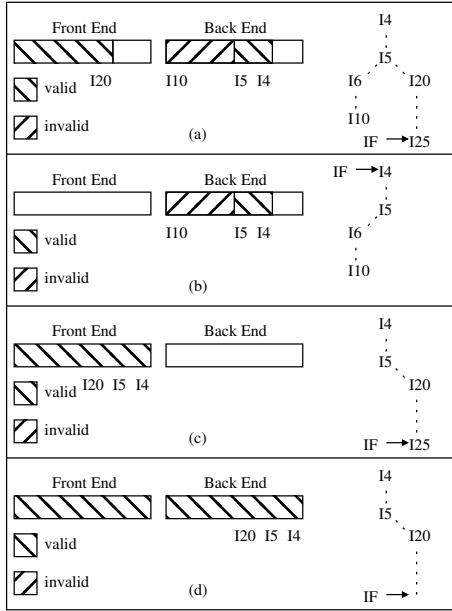

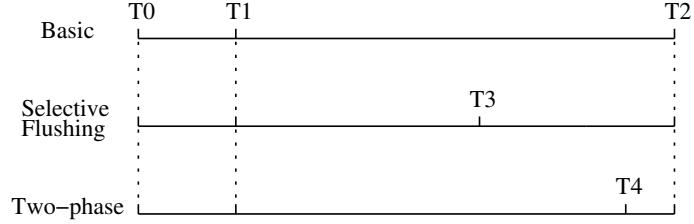

| 3.1  | A basic recovery mechanism . . . . .                                                                       | 63 |

| 3.2  | The issue to dispatch new instructions into the LSQ when it is not fixed . . . . .                         | 66 |

| 3.3  | The second phase of the recovery . . . . .                                                                 | 68 |

| 3.4  | Timeline of Recovery . . . . .                                                                             | 69 |

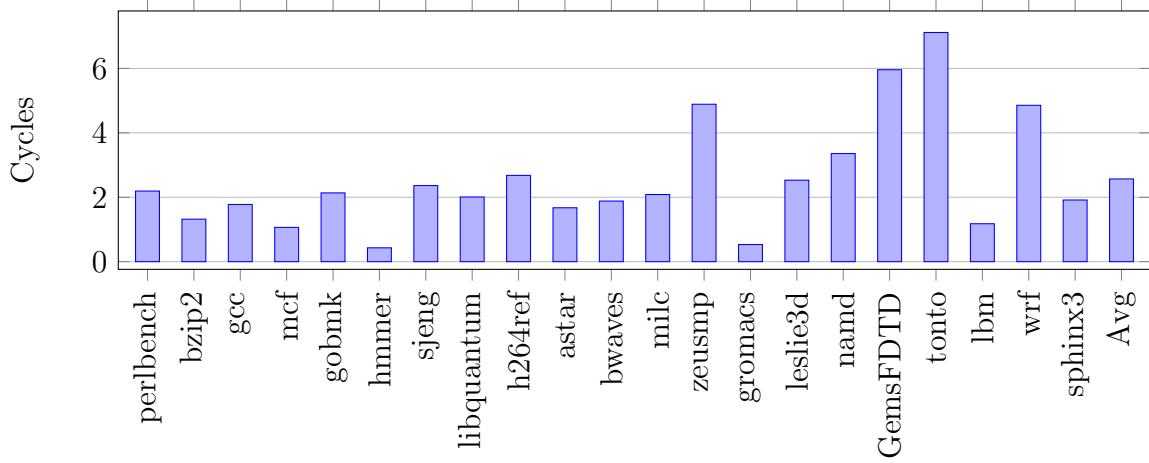

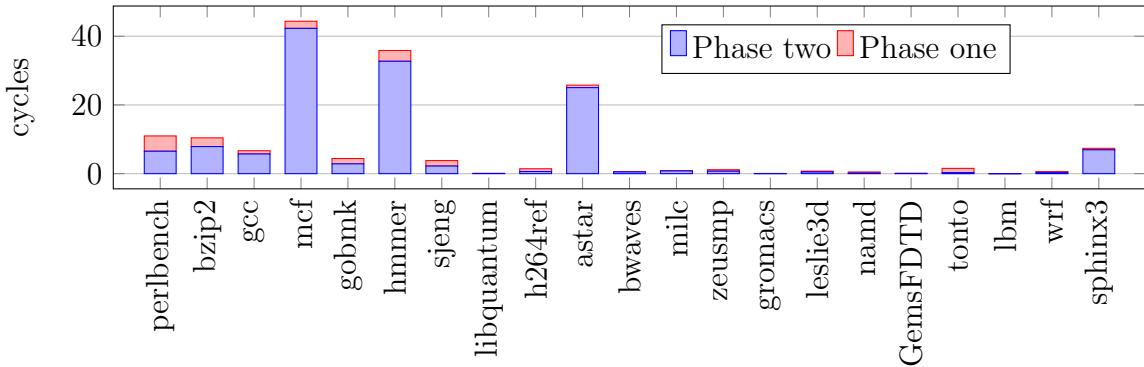

| 3.5  | Phase one to Phase two delay . . . . .                                                                     | 72 |

|      |                                                                                                         |     |

|------|---------------------------------------------------------------------------------------------------------|-----|

| 3.6  | The number of instructions between the cache miss load and the mis-prediction . . . . .                 | 73  |

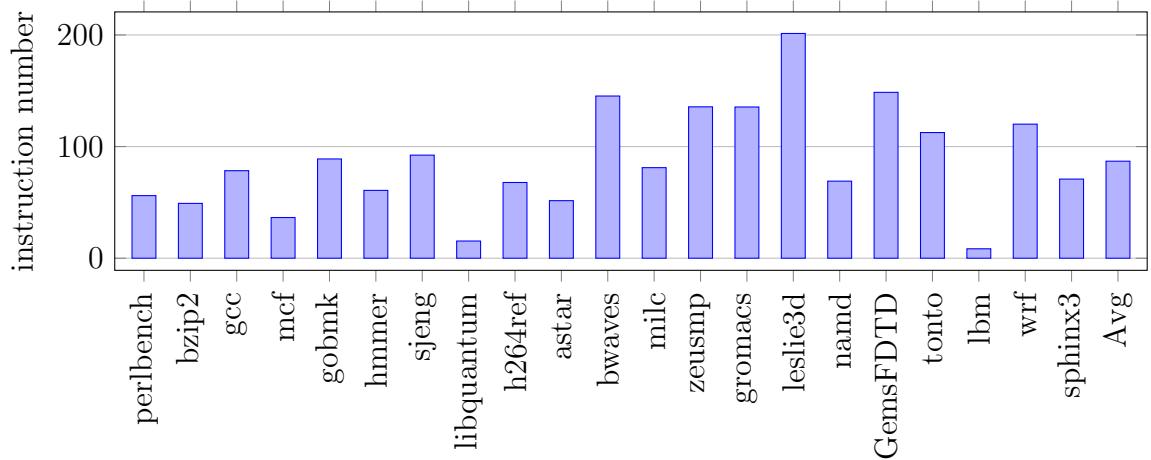

| 3.7  | Two phase recovery state machine . . . . .                                                              | 74  |

| 3.8  | Overwriting the prediction . . . . .                                                                    | 76  |

| 3.9  | Misprediction due to speculative recoveries . . . . .                                                   | 77  |

| 3.10 | The branch path tag for selective flushing . . . . .                                                    | 79  |

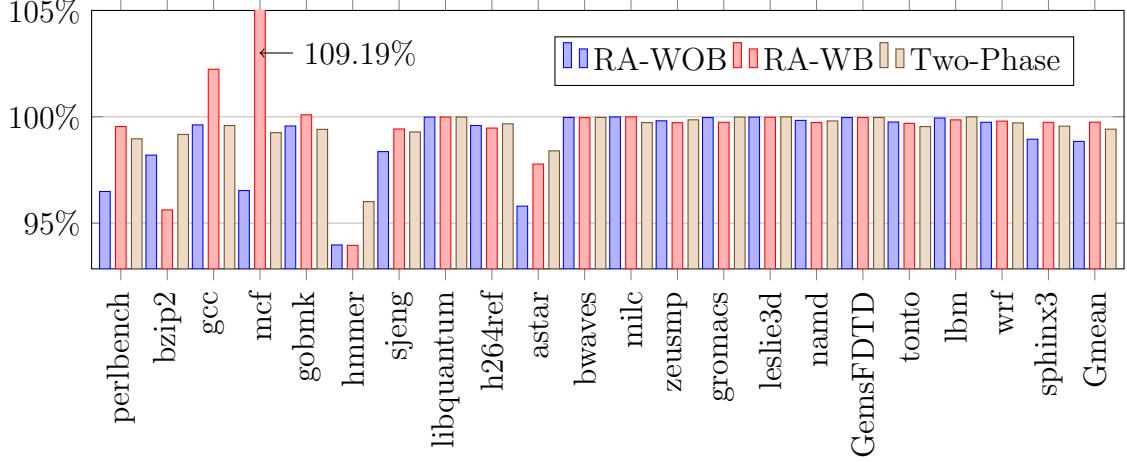

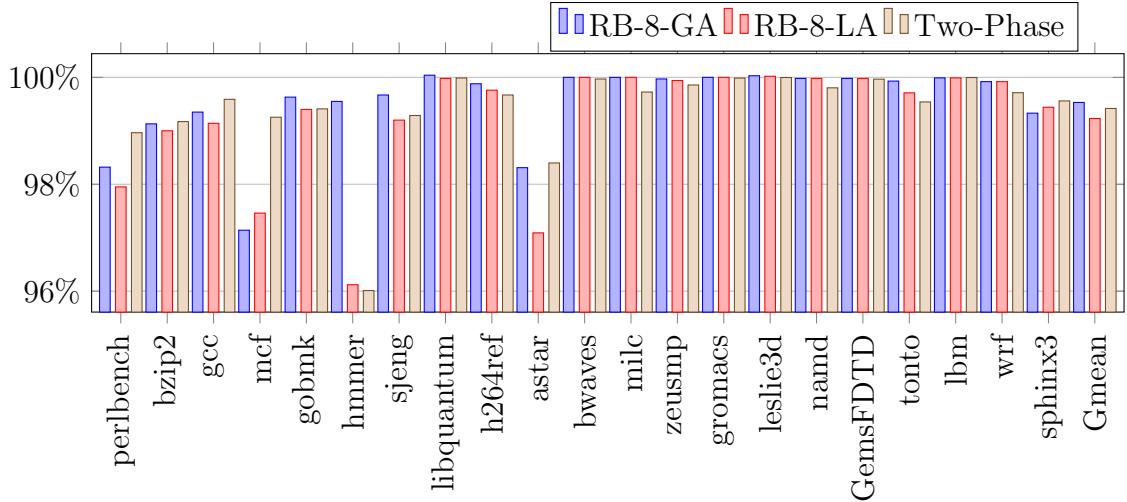

| 3.11 | Recover Afterwards with/without executing bogus instructions vs. Two-Phase, normalized to Inf . . . . . | 86  |

| 3.12 | RB-8-GA vs. RB-8-LA vs. Two-Phase, normalized to Inf . . . . .                                          | 88  |

| 3.13 | The extra cycles caused by Two-Phase compared with Inf . . . . .                                        | 89  |

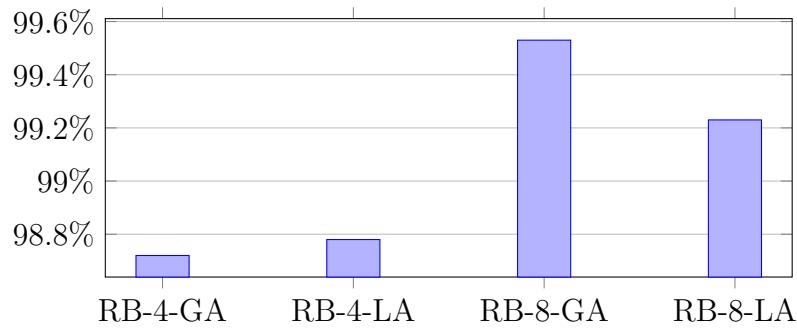

| 3.14 | The Geometric mean of different checkpoint allocation algorithms, normalized to Inf. . . . .            | 90  |

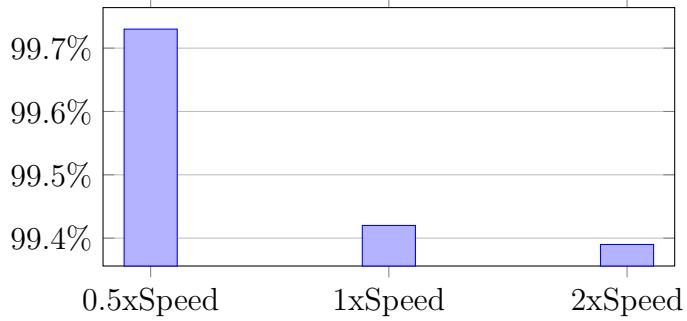

| 3.15 | The Geometric mean on different memory speed, normalized to Inf. . . . .                                | 91  |

| 3.16 | The Geometric mean on different rob size, normalized to Inf. . . . .                                    | 91  |

| 3.17 | The Geometric mean on different issue width, normalized to Inf. . . . .                                 | 92  |

| 4.1  | Control Dependence/Independence . . . . .                                                               | 97  |

| 4.2  | CDCF . . . . .                                                                                          | 108 |

| 4.3  | Passing Loop Microarchitecture Block Diagram . . . . .                                                  | 110 |

| 4.4  | Recovery through walking . . . . .                                                                      | 118 |

| 4.5  | Detecting the damaged register mappings . . . . .                                                       | 120 |

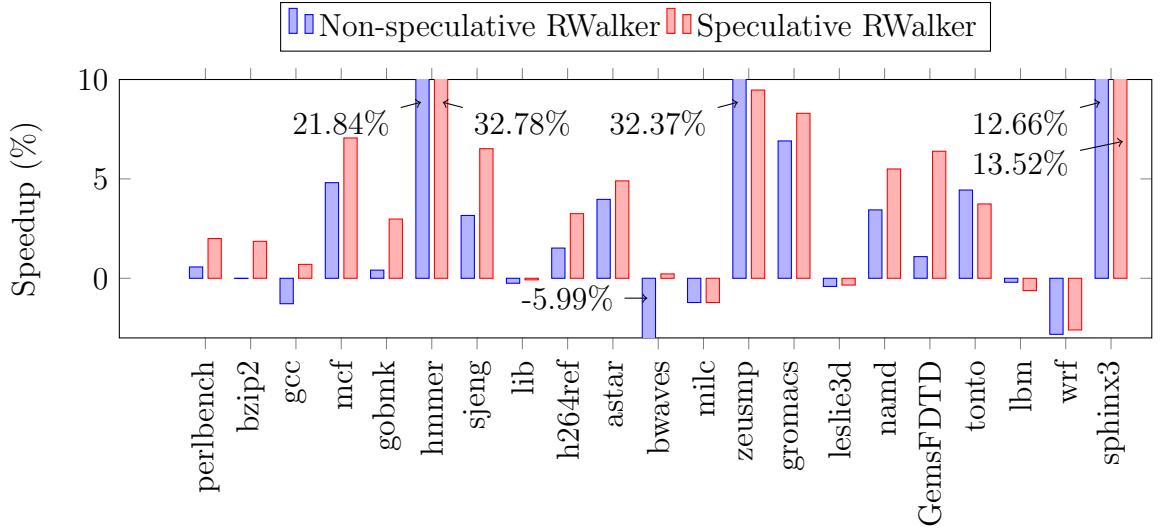

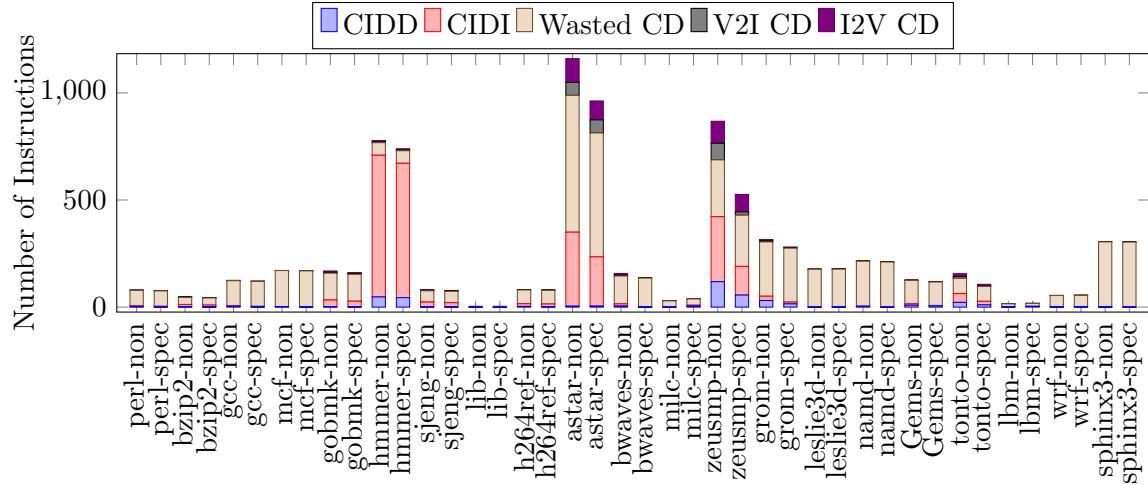

| 4.6  | Spec 2006 IPC speedup . . . . .                                                                         | 125 |

|      |                                                                                      |     |

|------|--------------------------------------------------------------------------------------|-----|

| 4.7  | Number of affected instructions per 1000 valid committed instructions                | 126 |

| 4.8  | Speedup if all instructions retired are valid . . . . .                              | 127 |

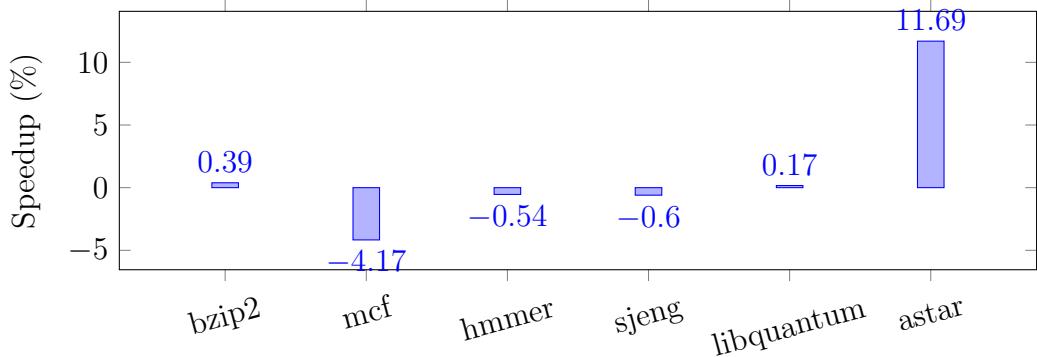

| 4.9  | The geometric speedup over different configurations for integer benchmarks . . . . . | 129 |

| 5.1  | OC dependence caused strict ordering. . . . .                                        | 141 |

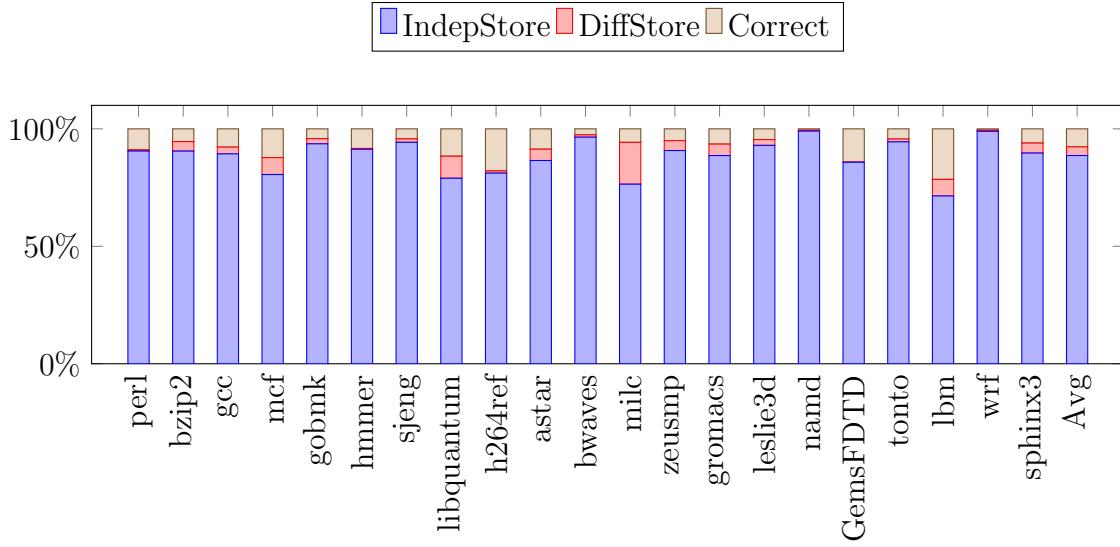

| 5.2  | Load instruction distribution . . . . .                                              | 142 |

| 5.3  | Delayed loads vs. bypassing loads . . . . .                                          | 143 |

| 5.4  | Three different ways to read data for loads. . . . .                                 | 144 |

| 5.5  | Memory dependence prediction results over low confidence loads . . . . .             | 147 |

| 5.6  | DMDP Microarchitecture . . . . .                                                     | 148 |

| 5.7  | Memory Cloaking . . . . .                                                            | 154 |

| 5.8  | Memory predication insertion . . . . .                                               | 156 |

| 5.9  | The producer counter . . . . .                                                       | 158 |

| 5.10 | Load re-execution incurred by silent store . . . . .                                 | 160 |

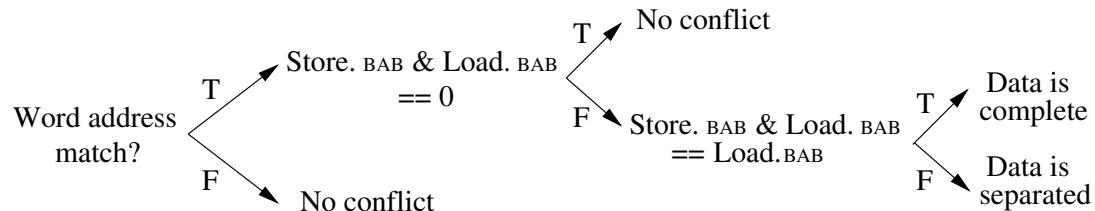

| 5.11 | The decision tree of partial-word forwarding detection . . . . .                     | 161 |

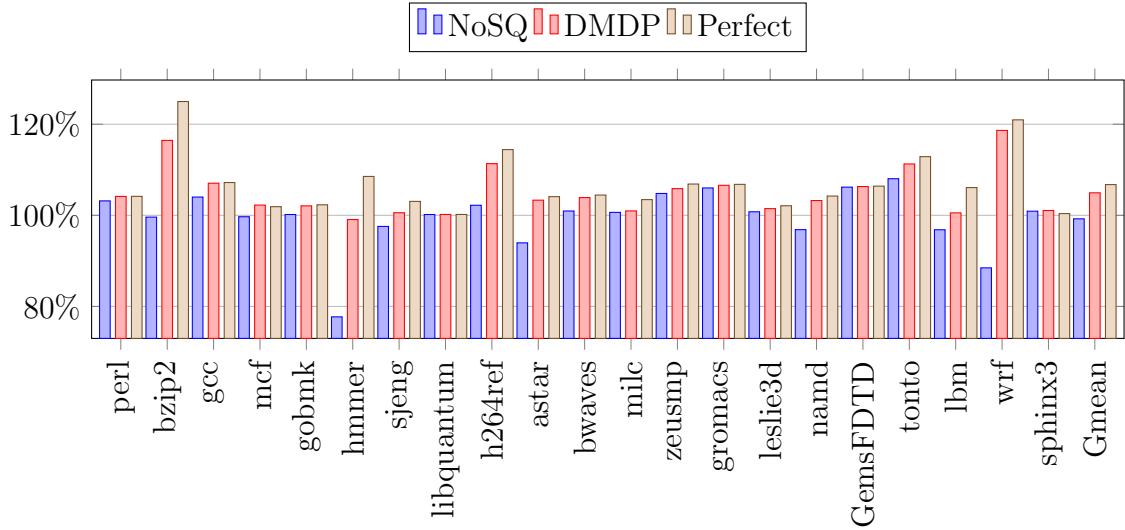

| 5.12 | Spec 2006 Speedup over the baseline . . . . .                                        | 169 |

| 5.13 | A <i>bzip2</i> code snapshot . . . . .                                               | 176 |

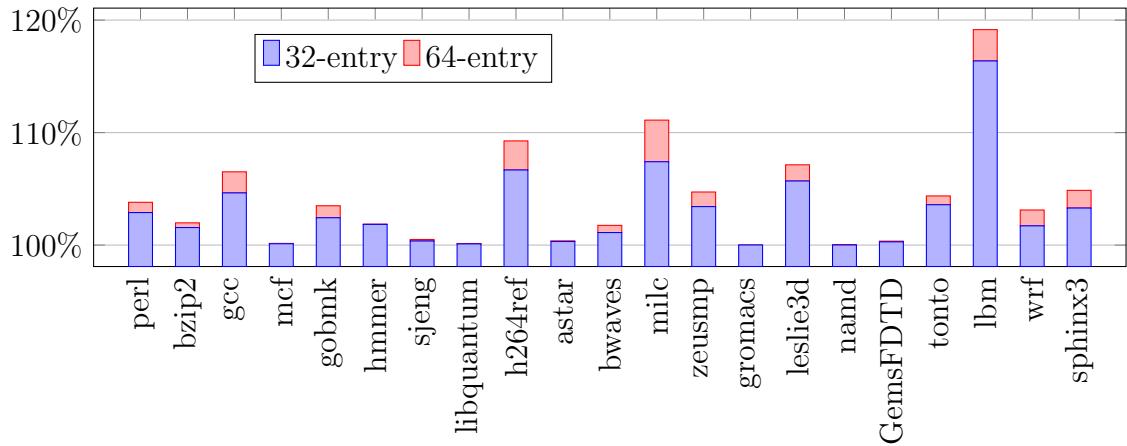

| 5.14 | 32,64-entry SB VS. 16-entry SB . . . . .                                             | 177 |

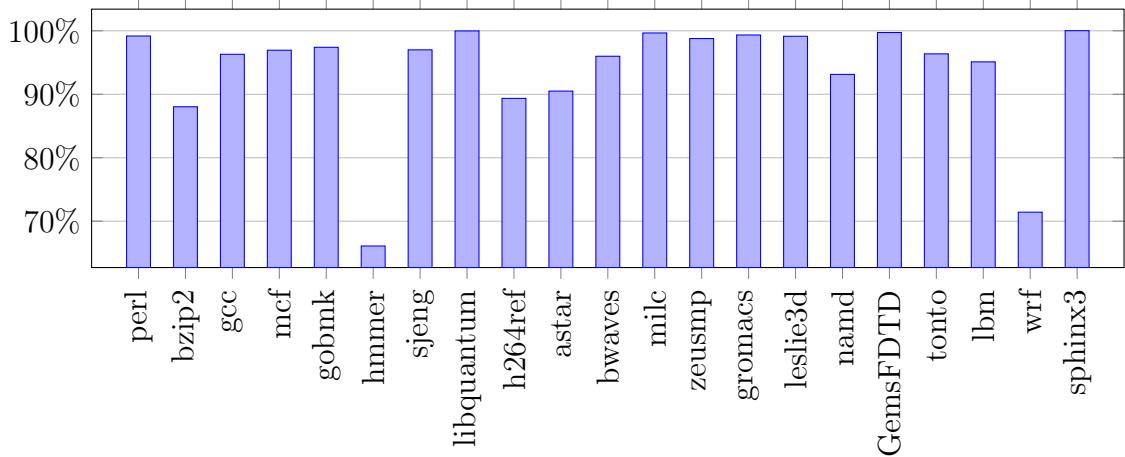

| 5.15 | The EDP of <b>DMDP</b> , normalized to <b>NoSQ</b> . . . . .                         | 179 |

# List of Tables

|     |                                                                                                                   |     |

|-----|-------------------------------------------------------------------------------------------------------------------|-----|

| 2.1 | The processor configurations . . . . .                                                                            | 50  |

| 2.2 | Energy consumption and Power dissipation in Mower and Baseline .                                                  | 57  |

| 3.1 | The average misspeculation recovery ratio and the corresponding back-end recovery time . . . . .                  | 71  |

| 3.2 | Processor Configuration . . . . .                                                                                 | 83  |

| 3.3 | The misspeculations which have checkpoints . . . . .                                                              | 88  |

| 3.4 | The EDP results of 2-phase with or without instruction reuse, compared with a 8-checkpoint architecture . . . . . | 93  |

| 4.1 | Spec 2006 Benchmark Suite . . . . .                                                                               | 122 |

| 4.2 | The Processor Configuration . . . . .                                                                             | 123 |

| 4.3 | The branch predictor performance . . . . .                                                                        | 124 |

| 4.4 | The percentage of increased mispredictions by non-speculative Passing Loop . . . . .                              | 128 |

| 4.5 | The speedup comparison between Gshare and TAGE, geometric mean over integer benchmarks . . . . .                  | 129 |

| 4.6 | The speedup of different branch coverage (speculative RWalker) . .                                                | 130 |

|     |                                                                      |     |

|-----|----------------------------------------------------------------------|-----|

| 4.7 | The CIDD redundancy . . . . .                                        | 131 |

| 4.8 | The EDP compared with the baseline processor . . . . .               | 133 |

| 4.9 | Design Resource classification . . . . .                             | 134 |

| 5.1 | The difference between NoSQ and DMDP on different loads . . . . .    | 145 |

| 5.2 | Load re-execution policy for different loads. . . . .                | 159 |

| 5.3 | Baseline Processor Configuration . . . . .                           | 167 |

| 5.4 | Average execution time of all loads . . . . .                        | 171 |

| 5.5 | Average execution time of low confidence loads . . . . .             | 173 |

| 5.6 | Memory dependence misprediction rate . . . . .                       | 174 |

| 5.7 | Load re-execution related stalls per 1k committed instructions . . . | 175 |

## **Author Contribution Statement**

The work in Chapter 2 was published in Proceedings of the 29th ACM on International Conference on Supercomputing. I am the first author of the publication and I contributed all of the ideas and the evaluations of the work.

The work in Chapter 3 will be published in Proceedings of the 32nd ACM on International Conference on Supercomputing. I am the first author of the publication and I contributed all of the ideas and the evaluations of the work.

The work in Chapter 5 will be published in Proceedings of the 45th Annual International Symposium on Computer Architecture. I am the first author of the publication and I contributed all of the ideas and the evaluations of the work.

## List of Abbreviations

|       |                                      |

|-------|--------------------------------------|

| ROB   | Reorder Buffer                       |

| RS    | Reservation Station                  |

| LSQ   | Load-Store Queue                     |

| RAT   | Register Alias Table                 |

| F-RAT | Front-end Register Alias Table       |

| R-RAT | Retirement Register Alias Table      |

| CD    | Control Dependent                    |

| CI    | Control Independent                  |

| CIDD  | Control Independent Data Dependent   |

| CIDI  | Control Independent Data Independent |

| RISC  | Reduced Instruction Set Computer     |

| CISC  | Complex Instruction Set Computer     |

| ILP   | Instruction Level Parallelism        |

| TLP   | Thread Level Parallelism             |

| BTB   | Branch Target Buffer                 |

| PC    | Program Counter                      |

| BHR   | Branch History Register              |

| PTH   | Pattern History Table                |

|      |                                       |

|------|---------------------------------------|

| RAS  | Return Address Stack                  |

| SSID | Store Set ID                          |

| SSIT | Store Set ID Table                    |

| LFST | Last Fetched Store Table              |

| WPE  | Wrong Path Events                     |

| CAM  | Content Addressable Memory            |

| ISA  | Instruction Set Architecture          |

| IPC  | Instructions Per Cycle                |

| EDP  | Energy Delay Product                  |

| CFG  | Control Flow Graph                    |

| LLC  | Last Level Cache                      |

| MPKI | Mispredictions Per 1k Instructions    |

| DDG  | Dynamic dependency graph              |

| DMDP | Dynamic Memory Dependence Predication |

# Abstract

Modern superscalar processors highly rely on the speculative execution which speculatively executes instructions and then verifies. If the prediction is different from the execution result, a misspeculation recovery is performed. Misspeculation recovery penalties still account for a substantial amount of performance reduction. This work focuses on the techniques to mitigate the effect of recovery penalties and proposes practical mechanisms which are thoroughly implemented and analyzed.

In general, we can divide the misspeculation penalty into four parts: **misspeculation detection delay**; **stale instruction elimination delay**; **state restoration delay** and **pipeline fill delay**. This dissertation does not consider the detection delay, instead, we design four innovative mechanisms. Some of these mechanisms target a specific recovery delay whereas others target multiple types of delay in a unified algorithm.

Mower was designed to address the **stale instruction elimination delay** and the **state restoration delay** by using a special walker. When a misprediction is detected, the walker will scan and repair the instructions which are younger than the mispredicted instruction. During the walking procedure, the correct state is restored and the stale instructions are eliminated.

Based on Mower, we further simplify the design and develop a Two-Phase recovery mechanism. This mechanism uses only a basic recovery mechanism except for the case in which the retire stage was stalled by a long latency instruction. When the retire stage is stalled, the second phase is launched and the instructions in the pipeline are re-fetched. Two-Phase mechanism recovers from an earlier point in the program and overlaps the recovery penalty with the long latency penalty.

In reality, some of the instructions on the wrong path can be reused during the recovery. However, such reuse of misprediction results is not easy and most of the time involves significant complexity. We design Passing Loop to reduce the **pipeline fill delay**. We applied our mechanism only for short forward branches which eliminates a substantial amount of complexity.

In terms of memory dependence speculation and associated delays due to memory ordering violations, we develop a mechanism that optimizes store-queue-free architectures. A store-queue-free architecture experiences more memory dependence mispredictions due to its aggressive approach to speculations. A common solution is to delay the execution of an instruction which is more likely to be mispredicted. We propose a mechanism to dynamically insert predicates for comparing the address of memory instructions, which is called “Dynamic Memory Dependence Predication” (DMDP). This mechanism boosts the instruction execution to its earliest point and reduces the number of mispredictions.

# Chapter 1

## Introduction

In recent years, more and more processor cores are integrated on a single chip to exploit more thread level parallelism. During this period, it became clear to processor designers that the clock frequency can no longer be increased due to physical limitations. About ten years ago, we had Intel Pentium 4 (Cedar Mill) which was running under 3.6GHz at 65nm process node. Nowadays the top of the line desktop processor, Intel Skylake, is working under 4GHz at 14nm process node. We can have more transistors on a single die, but we can not make the transistors switch faster. On the other hand, it is inefficient to invest all of the on-chip resources on a single processor core in terms of performance and energy. Given the same amount of resources, a 2-core processor can easily outperform a single core processor in many parallel applications.

As a result, the number of cores per processor continued to increase gradually through the years. From the industry side, we saw 2-core, 4-core and 8-core processors released to the market. From the academic side, 100-core, 1000-core processors are foreseen in the future landscape [1, 2]. Surprisingly, the number of the cores haven't changed for a long time since the first 8-core processor was introduced, as the dominant desktop processor currently available is still an 8-core processor. Does multi-core processor fail the future computer architecture design? We need to take one step back to analyze the performance model first for a better understanding.

*Amdahl's Law* [3] is introduced to explain how parallelism helps to improve the performance. *Amdahl's Law* separates the program execution into 2 parts, one part that can be parallelized and the other that can not. The overall speedup is then expressed by formula (1.1), where  $f$  is the fraction of the program which can be parallelized by a factor of  $S$ . Ideally, if the parallelized section takes no time to execute, it yields the second equation (1.2). Obviously, the roof of the speedup is constrained by the sequential code in the program.

$$Speedup(f, S) = \frac{1}{(1 - f) + \frac{f}{S}} \quad (1.1)$$

$$Speedup(f, S)_{S \rightarrow \infty} = \frac{1}{(1 - f)} \quad (1.2)$$

*Amdahl's Law* has been used to study the performance of multi-core processors extensively. In [4, 5], three different multi-core processor models were evaluated, namely, Symmetric, Asymmetric and Dynamic. Symmetric means all of the processor cores have the same resources. Asymmetric means a big core is coupled with several small cores. Dynamic means the processor can form a single super-core during the serial execution and can be decoupled to multiple cores during parallel execution. The conclusion of these papers are that even for a parallelism rich application, it is still worthwhile to build an “energy inefficient” big core, since every second it saves from the serial section can be translated to more parallel work in the rest of the “energy efficient” small cores. In typical parallel programs, the parallel part of the program is thoroughly optimized but the serial part remains on the critical path. Therefore, this dissertation focuses on the techniques to optimize the single-thread program performance in the superscalar processor.

Speculative execution is the key component for modern superscalar processors to reach high performance. Predicting branch direction and the target address [6, 7, 8] helps the processor to keep fetching subsequent instructions when the branch is not resolved. Value prediction [9, 10, 11] is used to overcome the data dependence limitation in exploiting instruction level parallelism (ILP). Memory dependence prediction [12, 13] is designed to bridge the in-flight stores and the loads. With the given progress of speculative execution, it is believed that more and other types of speculations will be involved in designing future architectures.

Although speculation is a powerful mechanism for exploiting ILP, if the speculation is wrong, the instructions fetched after the misspeculation have to be eliminated. The processor has to roll back to the misspeculation point and restart fetching from the correct path. There are two ways to improve the performance, either improving the speculation accuracy or recovering the misspeculations more quickly. The former approach has been broadly investigated and there is not much room left for improvement. For example, Geometric History Length branch predictor [14, 15] provides very high branch prediction accuracy and the memory dependence predictor [16, 17, 18] achieves very high memory dependence prediction accuracy. The latter approach, namely, recovering from a misspeculation has not been thoroughly investigated and this dissertation concentrates on techniques to recover misspeculations quickly and efficiently.

The rest of this chapter is organized as follows. Section 1.1 gives background information about superscalar processors. We then describe speculation mechanisms used in superscalar processors in Section 1.2. Widely used recovery mechanisms are discussed in Section 1.3. Finally, we give a taxonomy of recovery penalties in Section 1.4.

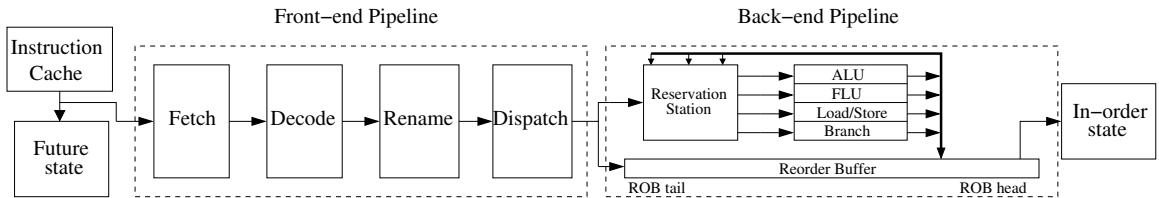

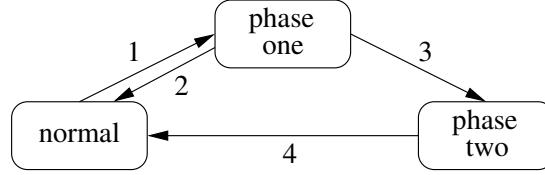

## 1.1 A Superscalar Processor

A typical superscalar processor is composed of two major parts: the front-end and the back-end, as shown in Figure 1.1. The front-end of the pipeline is in charge of fetching, decoding, renaming and dispatching. The back-end of the pipeline is in charge of instruction execution and retirement. The instructions which are in-flight in the pipeline (front-end and back-end) are speculative. Roughly speaking, their results are invisible to the outside until they are retired. Thereafter, the results are committed to the in-order state which contains all the valid execution outcomes. The future state in the figure represents the state obtained by combining the in-order state with the speculative instructions left in the pipeline.

**Figure 1.1:** The block diagram of a superscalar processor

### 1.1.1 The Front-end

The front-end follows the program order so that the instructions flow sequentially similar to a queue. The fetch unit first fetches instructions from the instruction

cache. The fetched instructions are then decoded. For a fixed-length instruction set, the decode stage is very straightforward. For a variable-length instruction set, decoding is much more difficult. Since the length of each instruction varies, most processors require a multi-cycle decode stage. The next stage is renaming and both instruction operands and destination are mapped to the physical space from the logical space. The details of the renaming process is explained later in Section 1.1.3. The last stage dispatches instructions to the corresponding components in the back-end.

### 1.1.2 The Back-end

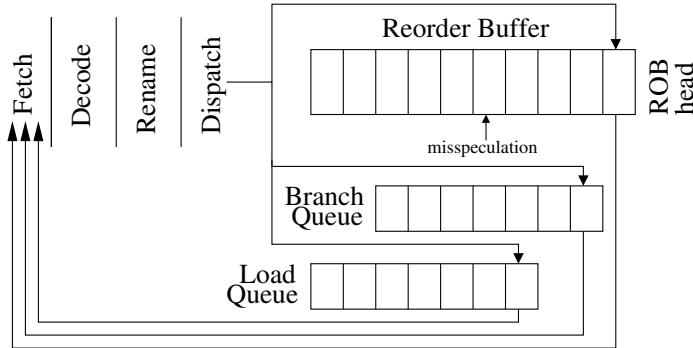

The back-end of the pipeline is constructed to execute instructions in an out-of-order manner to exploit Instruction Level Parallelism (ILP). An instruction from the front-end is assigned to Reservation Station (RS) and Reorder Buffer (ROB) in parallel. RS acts like a shelf which maintains all the unexecuted instructions. Once the operands of an instruction are ready, the instruction is woken up to execute. Therefore, the execution obeys the data dependence and may change the original program order.

The ROB maintains the instruction state before they are retired. Instructions are allocated to ROB positions following the program order and they retire in program order as well. However, only completed instructions are allowed to retire. When an instruction is executed, its completion bit in ROB is set. Hence, an executed instruction is not retired until all preceding instructions are retired.

### 1.1.3 Register Alias Table

Before an instruction is dispatched to the back-end, it has to be renamed. Every destination logical register is renamed to a dedicated physical register in order to eliminate false data dependencies. A simple example is illustrated in Figure 1.2.

| logical space      | RAT            | RAT                             | RAT                                        | RAT                                                    | RAT                                                    |

|--------------------|----------------|---------------------------------|--------------------------------------------|--------------------------------------------------------|--------------------------------------------------------|

| I1:\$1 = \$2 + \$3 | \$1   P7       | \$1   P7   P1                   | \$1   P1                                   | \$1   P1   P3                                          | \$1   P3                                               |

| I2:\$2 = \$1 - \$3 | \$2   P10      | \$2   P10                       | \$2   P2                                   | \$2   P2                                               | \$2   P2                                               |

| I3:\$1 = \$4       | \$3   P11      | \$3   P11                       | \$3   P11                                  | \$3   P11                                              | \$3   P11                                              |

| I4:\$4 = 200       | \$4   P9       | \$4   P9                        | \$4   P9                                   | \$4   P9                                               | \$4   P9                                               |

|                    | →              | →                               | →                                          | →                                                      | →                                                      |

|                    | P1 = P10 + P11 | P1 = P10 + P11<br>P2 = P1 - P11 | P1 = P10 + P11<br>P2 = P1 - P11<br>P3 = P9 | P1 = P10 + P11<br>P2 = P1 - P11<br>P3 = P9<br>P4 = 200 | P1 = P10 + P11<br>P2 = P1 - P11<br>P3 = P9<br>P4 = 200 |

**Figure 1.2:** From logical register space to physical register space

The rename process consists two steps. First, the operands are renamed by reading the Register Alias Table (RAT). Second, the destination register of the instruction is assigned a new physical register from the free register pool and the new mapping is updated in the RAT. In the figure, the first instruction reads the current mappings of  $\$2$  and  $\$3$  and the instruction's destination register is assigned to  $P1$ . The updated mapping of  $\$1$  is written back to the RAT to replace the old one ( $P7$ ). The following instructions can find the correct physical register of  $\$1$  through RAT. The fully renamed code is shown on the right of the figure as well as the corresponding RAT contents.

## 1.2 Speculative Execution

Speculative execution is a key component of superscalar processors. Generally speaking, an instruction's result is predicted upfront before its execution. Therefore, the dependent instructions are executed earlier with this prediction. In this work, two major speculation techniques have been evaluated, branch prediction and memory dependence prediction.

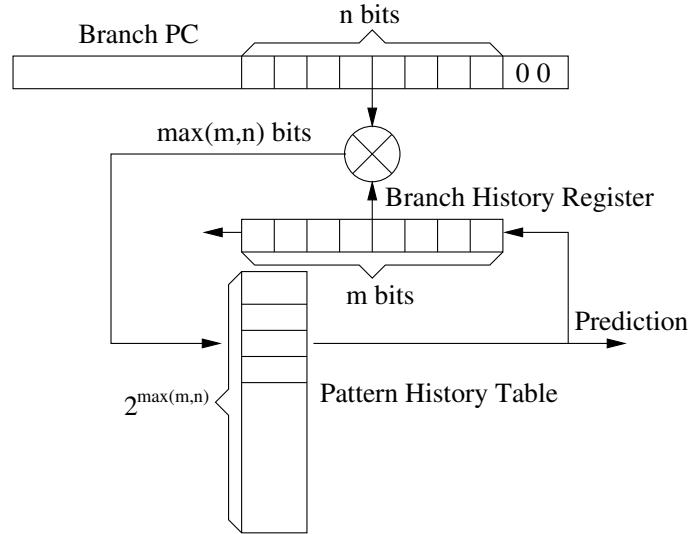

### 1.2.1 Branch Prediction

The branch result is unknown until it is resolved. However, the fetch unit needs to know the result immediately in order to fetch the subsequent instructions. Consequently, the branch is predicted once it is fetched. A common superscalar processor has a branch predictor to predict the direction of the branch instruction and a Branch Target Buffer (BTB) to predict the target address when the branch is predicted to be taken.

Typically the branch predictor considers the history information to make the prediction. Both the local history and the global history are considered. The local history can simply be the Program Counter (PC) of the branch or it can be a recorded history

of this branch. The global history is usually the most recent branch predictions.

**Figure 1.3:** Gshare branch predictor

Figure 1.3 shows the structure of a correlating branch predictor called **Gshare** branch predictor. The Pattern History Table (PHT) is used to provide the prediction and it is indexed by exclusive ORing the branch PC and the Branch History Register (BHR). BHR keeps the recent branch prediction history. Every time a new prediction is made, the prediction is pushed into the BHR and the oldest prediction is eliminated. When a branch is mispredicted, the corresponding entry in PHT is updated. More advanced branch predictors are invented to consider a much larger number of history bits [19, 20].

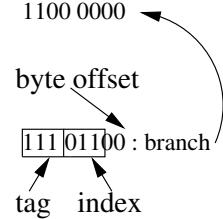

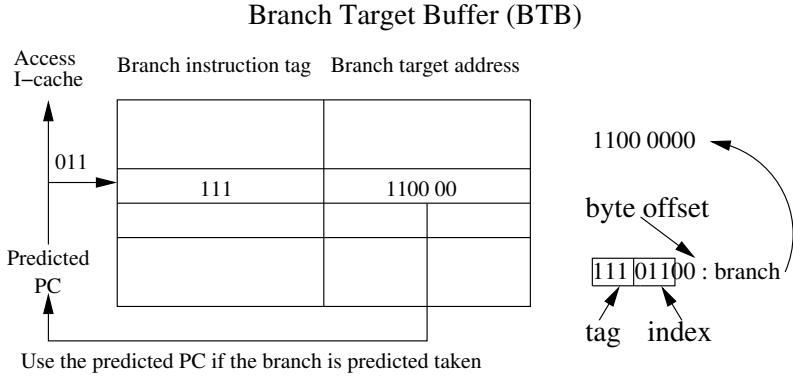

The Branch Target Buffer (BTB) [21] provides the target address when the branch is predicted taken. Figure 1.4 illustrates a simple BTB design which works as a cache. The low bits of the branch PC are used to index BTB and the corresponding

**Figure 1.4:** Branch Target Buffer

branch instruction tag entry contains the high bits. If the branch PC hits in BTB, the corresponding branch target address is read to fetch the subsequent instructions. In the figure, the branch located in *1110 1100* is predicted to jump to address *1100 0000*.

**Figure 1.5:** Return Address Stack

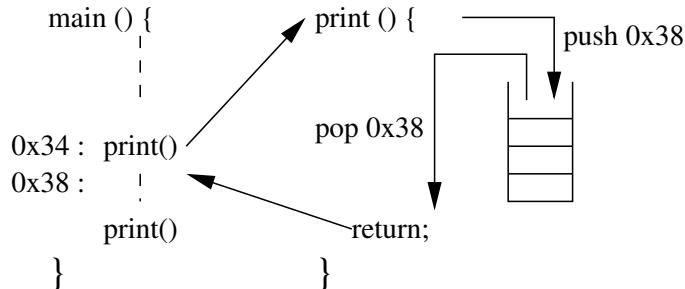

Other than the BTB, another dedicated component is designed to predict the return address of the function call, namely the Return Address Stack (RAS). Figure 1.5 shows a simple program in which the function “print” is called twice at different places. The return instruction in “print” has a single PC but two target addresses. A BTB does not work well when the target address varies and the RAS is designed

to address this issue. When the first “print” is called, the PC of the next instruction,  $0x38$ , is pushed into the RAS. When the return instruction is executed, the target address is popped out of the RAS. Since the RAS is a stack, it always provides the return address of the most recent function call.

### 1.2.2 Memory Ordering Prediction

Memory instructions are different from other instructions as the data dependencies are unknown until load and store are computed. A load instruction is dependent on a prior store when they access the same memory address. However, in superscalar processors, instructions are executed in an out-of-order manner which makes memory disambiguation very difficult.

For the purpose of bridging the in-flight stores and loads, a typical superscalar processor contains a store queue and a load queue. The store queue maintains all the in-flight stores in program order. Once a store’s operands are ready, the store address and the store data are written into the corresponding entry in the store queue. The load queue maintains all the in-flight loads in program order. When a load is executed, the load address is written into the corresponding entry in the load queue.

When a load is executed, it simultaneously sends its address to the cache and the store queue. If the store queue does not have any store instruction matching the

address, the data read from the cache is forwarded to the load. Otherwise, the closest preceding store's data is used.

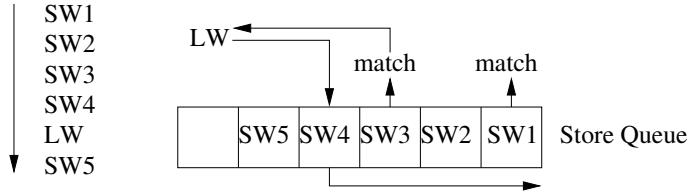

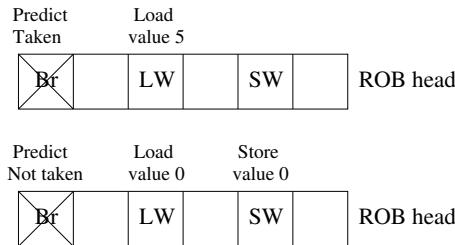

**Figure 1.6: Store Queue**

Figure 1.6 shows a simple example about how a load obtains its value from the store queue. The left side of the figure lists all the memory instructions in program order. When the load is decoded, the entry of the last store is kept with the load. In this example, **LW** knows the last store is **SW4** so the load only searches the stores which are older than **LW** (**SW1-SW4**). The youngest store is selected if there are multiple matching stores. In the figure, if both **SW3** and **SW1** match the address of **LW**, then **SW3** is selected. On the other hand, when a load is executed before a prior matching store updates the store queue, the load may read a wrong value and broadcast it to the dependent instructions. This load and the following instructions need to be re-executed. The memory ordering violation is detected through the load queue.

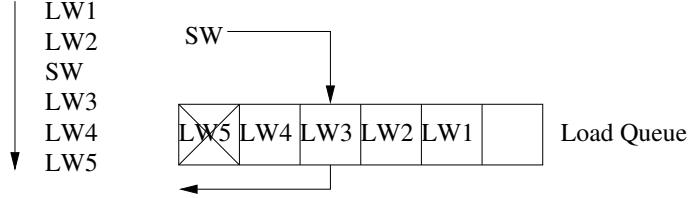

Figure 1.7 illustrates a load queue. The left side of the figure shows the original instructions following the program order. When **SW** is decoded, the location of the most recent load, **LW2**, is kept with the store. When a store updates the store queue,

**Figure 1.7:** Load Queue

it only searches the loads which are younger than **SW** in the load queue. Any load instructions that executed before the store and had the same address violates the memory ordering. In this example, **LW5** which has the same address is younger than **SW** and had executed before **SW**. Therefore, this load has been misspecified and a misspeculation recovery needs to be performed.

If a load executes without considering the prior stores, it is possible to have a memory ordering violation. However, if the load is forced to wait for all prior stores to execute, the resulting delay will be detrimental to the performance. Therefore, a feasible solution is to predict the dependencies for memory instructions. Roughly speaking, load instructions are blindly executed at the beginning assuming they are independent of prior store instructions. Once a dependence violation is detected, a correlation between the load and the conflicting store can be established. Thereafter, the load can wait for this particular store.

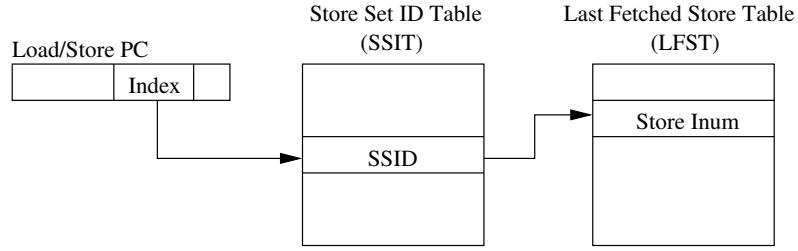

There are many mechanisms which maintain the correlations among load and store instructions, one such mechanism is the Store Set algorithm [16]. Store Set algorithm renames memory instructions using Store Set ID (SSID). If the store and the load

had collided before, they are assigned the same SSID. The load will have to wait if any prior store with the same SSID has not executed.

**Figure 1.8:** Store Set mechanism

Figure 1.8 illustrates the Store Set mechanism. Both store and load instructions get their SSIDs by reading the Store Set ID Table (SSIT). The store instruction uses its SSID to write a unique identity called Store Inum in the Last Fetched Store Table (LFST). The Store Inum is a hardware pointer such as the ROB entry number. The load instruction uses its SSID to read LFST to check if there is an in-flight store with the same SSID. If the store exists, the load can find the store using its Store Inum. Otherwise, the load can execute whenever the load address is known.

### 1.3 Misspeculation Recovery

Not every speculative execution is correct. Once a misspeculation happens, the recovery process is initiated: I) The branch predictor's state is restored back to the misspeculation point so that the correct instructions can be predicted properly; II)

The fetch engine redirects to the misspeculation point and fetches the valid instruction; III) The Register Alias Table (RAT) is reverted back to the misspeculation point so as to correctly rename the valid instructions; IV) The resources which are occupied by the invalid instructions are released. We have discussed two major types of misspeculations, branch mispredictions and memory dependence misspeculations. Although the same recovery process can be utilized for both types of misspeculations, memory dependence mispredictions can be handled by re-executing instructions which received the incorrect values, whereas in case of branch misspeculations incorrectly fetched instructions need to be eliminated from the pipeline.

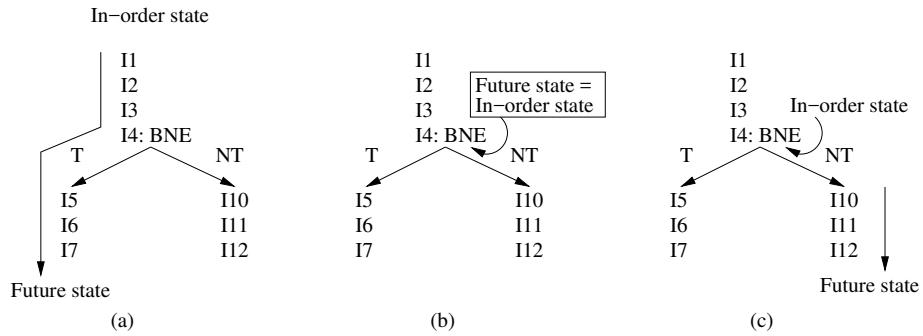

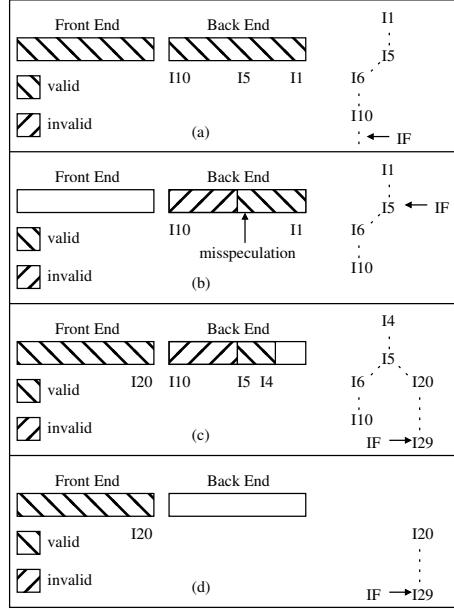

**Figure 1.9:** Branch misprediction recovery

Figure 1.9 shows a basic recovery process for a mispredicted branch. The process states described in Section 1.1 are also shown here. The in-order state represents the valid execution results. The future state represents the combination of the in-order state with the speculative state. In Figure 1.9(a), the branch **BNE** is predicted taken which turns out to be a misprediction. Therefore, instructions *I1-I4* are still valid but the following instructions *I5-I7* are invalid. The future state is damaged at this point,

so the fetch engine stops. The valid instructions are allowed to retire and update the in-order state. When the last valid instruction  $I_4$  is retired, the instructions left in the pipeline are all invalid and can be immediately eliminated. Simultaneously, the future state is restored back to the in-order state in Figure 1.9(b). Since the correct branch result is known, the fetch engine restarts to fetch the valid instructions  $I_{10}-I_{12}$  in Figure 1.9(c).

The basic recovery process for memory dependence misspeculation is similar. When a load instruction conflicts with a store instruction, the instructions before the load are still valid and retired. Remaining instructions are eliminated and the future state is rolled back to the misspeculation point. The misspecified load is re-executed and will retrieve the correct value since all prior stores have retired.

### 1.3.1 Recovering Branch Predictor State

After a branch misprediction, the branch predictor would have been updated with the wrong values. Without correcting the branch predictor state, new branch predictions will be very inaccurate. Therefore, the first task in recovery process is to repair the branch predictor state. Typically, Pattern History Table (PHT) is designed to be updated at the retire stage by only valid instructions. Hence, PHT does not need to be modified. Since the Branch History Register (BHR) and the Return Address

Stack (RAS) are speculatively modified, these components need to be repaired.

Although the BHR keeps the  $m$  most recent predictions in order to predict the next branch, in a real hardware design, BHR is made larger so that it can be rolled back to a previous position.

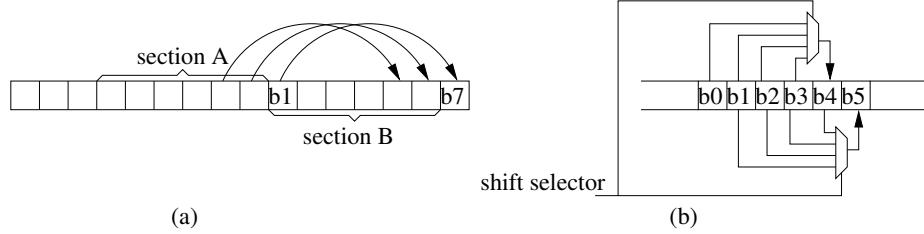

**Figure 1.10:** Recover Branch History Register

Figure 1.10(a) illustrates a BHR design in which the younger branches are listed to the right of the figure. When branch  $b1$  is predicted, section A in the BHR is the most recent branch history and this section is used to make a prediction. The following branches,  $b2-b7$ , are then predicted and pushed into the BHR. Branch  $b1$  is a misprediction, thus, the processor has to shift section A to the right in the BHR. Figure 1.10(b) shows a shifter design which can shift the BHR to the right by a variable number of bits.

The second part of the branch predictor recovery is the Return Address Stack (RAS) which is used to predict the return address from a function call. It is mentioned in [22] that it is possible to corrupt RAS during the misspeculation recovery. In most scenarios, a younger return instruction may overwrite an RAS entry which keeps

another return address. Therefore, there is no way to roll back to a previous point during the recovery.

Dixon et al. implemented a practical solution to fix RAS. They used the same technique from Register Alias Table (Section 1.1.3) to map RAS entries to physical registers. By doing this, two different return addresses which are written to the same RAS entry are mapped to two different physical registers. In the recovery, the processor only needs to restore the correct mapping to fix RAS. The method to restore the mapping is similar to the RAT correction which is described in Section 1.3.2.

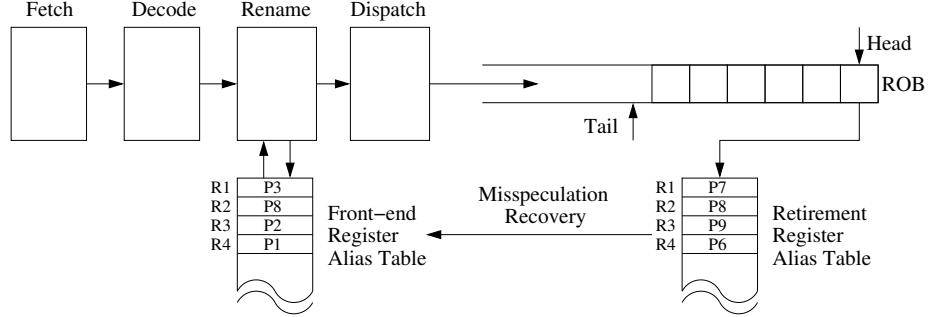

### 1.3.2 Restoring the Map Tables

We mentioned at the beginning of this section that the future state is restored by copying from the in-order state and RAT is repaired in this way. In most superscalar processors, there are two RATs serving different roles. The Front-end RAT (F-RAT) is located at the rename stage and is speculative. The Retirement RAT (R-RAT) is located at the retire stage which keeps the in-order state [23]. During the recovery, R-RAT is copied to F-RAT when the misspeculated instruction is retired. This mechanism is shown in Figure 1.11.

**Figure 1.11:** Recover Register Alias Table

### 1.3.3 Eliminating Stale Instructions

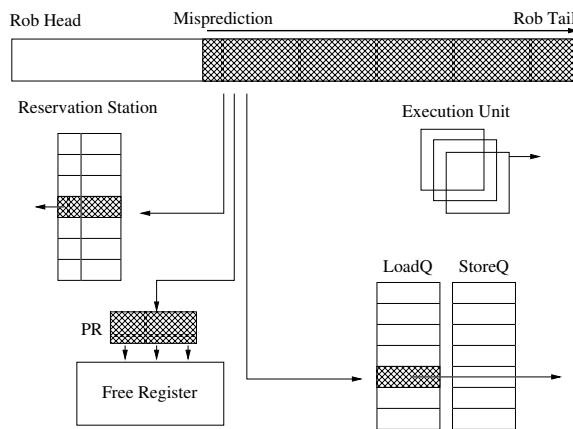

The instructions following the misspeculated instruction are marked as stale and cannot change the in-order state. The resources which were occupied by the stale instructions are released during recoveries. When a misspeculation is detected, the instructions left in the front-end are all stale. Consequently, the front-end is reset to eliminate all stale instructions. The situation in the back-end is different since it is mixed with valid and stale instructions. The basic recovery mechanism will not reset the back-end until all valid instructions are retired.

## 1.4 Recovery Penalty Analysis

We have described the basic recovery mechanism. In this section, the recovery penalty resulting from misspeculations is analyzed and a taxonomy of misspeculation recovery

is given. This work divides the recovery penalty into different parts. These are the **misspeculation detection delay**, **stale instruction elimination delay**, **state restoration delay** and finally **pipeline fill delay**. For each part, we also give some of the related work in this section.

#### 1.4.1 Misspeculation Detection Delay

A speculative instruction does not know its result until it is fetched, decoded, renamed and finally executed. Therefore, the misspeculation detection delay is the time spent for misspeculation to be detected since that misspeculation was fetched. In most cases, it is very difficult to reduce the misspeculation detection delay since the tasks associated with each instruction's execution cannot be reduced.

Armstrong et al. presented a mechanism to speculatively predict a misspeculation [24] by observing Wrong Path Events (WPE). WPE is classified into two categories: memory instructions and control flow instructions. Memory instructions include dereferences of NULL pointers, reads or writes to unaligned addresses, writes to a read-only page, reads from an executable page or TLB misses, etc. Control flow instructions include branch mispredictions and RAS underflow. When a WPE is observed, it is highly likely that there is a misspeculation. Therefore, even if the exact misspeculation point is not found, their mechanism can predict the misspeculation point and start to recover before the misspeculation is resolved.

### 1.4.2 Stale Instruction Elimination Delay

Section 1.3.3 has described a basic mechanism to eliminate stale instructions and release the occupied resources. This mechanism does not eliminate stale instructions until all the valid instructions are retired. If the retirement is halted by some long latency operations, such as a cache missing load instruction, the elimination delay may significantly affect the overall performance.

McIlvaine et al. designed a specific rename algorithm [25] to assign a dedicated **branch flush tag** to each branch. The tag is a bit vector which has only one bit set to high. Hence, the width of the bit vector is equivalent to the number of tags. Other than the **branch flush tag**, a **branch path tag** is also implemented. Each instruction has its own branch path tag indicating which unresolved branches it is dependent on. When a branch misprediction is detected, its branch flush tag is broadcast and the instructions which are dependent on this branch are selectively flushed.

### 1.4.3 State Restoration Delay

The basic recovery mechanism explained in Section 1.3 restores the future state by copying the in-order state and this is the state restoration delay. The retirement

of the valid instructions also constrains the state restoration delay due to the same reason described before.

Checkpointing architectures [26, 27] were designed and developed to construct a larger instruction window. This mechanism also shortens the state restoration delay. When a branch is at the rename stage, a copy of the current F-RAT is kept as a checkpoint. If this branch is mispredicted, the checkpoint is used to instantly restore the F-RAT.

To keep a checkpoint for every branch is very costly. So a practical solution is to allocate a checkpoint only when a particular branch is likely to be mispredicted. A confidence predictor is used to predict how likely the coming branch is going to be a misprediction.

#### 1.4.4 Pipeline Fill Delay

A misspeculation may cause the processor to eliminate a substantial amount of stale instructions. It takes many cycles to fill an empty pipeline and this is the pipeline fill delay. One of the solutions is to reuse the stale instruction computations.

Usually a program forks at the branch instruction and joins at a later point. The instructions fetched after the join point are control independent of the branch result. In other words, the control independent instructions are always executed regardless

of the branch direction. In consequence, if the branch is mispredicted, some of the control independent instruction results can be reused. Such reuse mechanisms exploit Control Independence [28] of instructions.

## 1.5 Summary

In this chapter, we went over the basic components of a superscalar processor and explained the speculative execution including branch prediction and memory dependence speculation. We also elaborated in detail, a basic recovery mechanism and outlined the recovery process to restore branch predictor, return address stack and the front-end RAT. We also provided a taxonomy which classifies the recovery penalty into four parts: **misspeculation detection delay; stale instruction elimination delay; state restoration delay; pipeline fill delay**. In the rest of the dissertation, the proposed mechanisms are illustrated and analyzed thoroughly to address each of these delays.

# Chapter 2

## Mower : A Walking-based

## Misspeculation Recovery

### Mechanism

#### 2.1 Overview

In the previous chapter we have described a basic recovery mechanism and presented a taxonomy of misspeculation recovery penalties. In this taxonomy, one of the delays is the **state restoration delay**, such as restoring the correct F-RAT. The basic

---

<sup>0</sup>The material contained in this chapter was previously published in Proceedings of the 29th ACM on International Conference on Supercomputing (ICS '15) [29]. The copyright permission is listed in Appendix A.

recovery mechanism outlined in Chapter 1 does not recover F-RAT until all the valid instructions are retired. Therefore, the state restoration delay is highly dependent on the speed of valid instruction retirement. If the retirement is impeded by some long latency operation then the misspeculation penalty is exacerbated.

For the purpose of breaking the dependence between the recovery penalty and the valid instruction retirement, many innovative techniques were proposed. These techniques can be classified into two categories: walking and checkpointing. We briefly review both techniques in this section and bring in the concept of Mower, a walking-based recovery mechanism.

### 2.1.1 Recovering F-RAT by Walking

F-RAT contains the correct mapping table at the misspeculation point and the updates done by the instructions after the misspeculation point. A easy approach to restore F-RAT is to undo all the updates after the misspeculation. This mechanism acts like a walker walking back toward the misspeculation. When it is walking, any updates made by instructions to F-RAT is undone.

Moudgill et al. first designed a register renaming algorithm which is similar to the one widely used in contemporary superscalar processors [30]. Their work consists

of a register mapping algorithm, a physical register release algorithm and an algorithm to handle precise interrupts. In order to recover F-RAT, a **history buffer** is implemented to keep the old physical register mapping of each instruction. During recovery, correct mapping table is restored by using the **history buffer** contents.

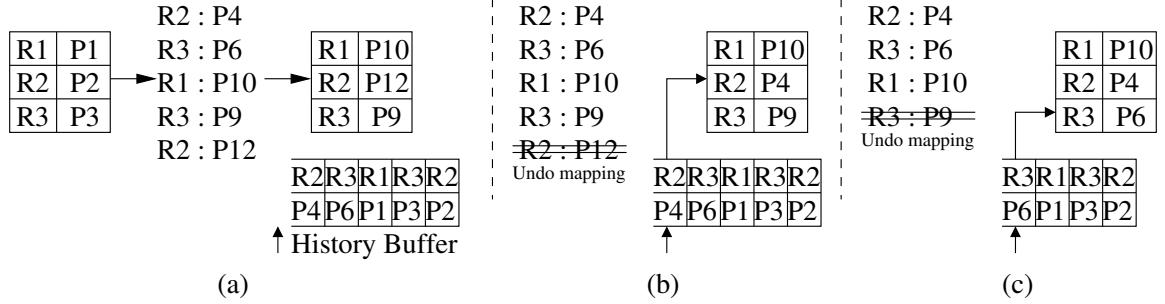

**Figure 2.1:** Restoring the mapping table by history buffer

Figure 2.1 is a simple example demonstrating how the history buffer mechanism works.

Initially, **R1**, **R2** and **R3** are mapped to **P1**, **P2** and **P3** respectively in Figure 2.1(a).

Whenever an instruction is renamed, its newly assigned physical register modifies the mapping table. Simultaneously, the old physical register number is pushed into the **history buffer**. For example, the first instruction maps **R2** to **P4** and the old mapping, **R2** to **P2**, is pushed into the **history buffer**. The resulting mapping table and **history buffer** contents are depicted on the right side of the figure.

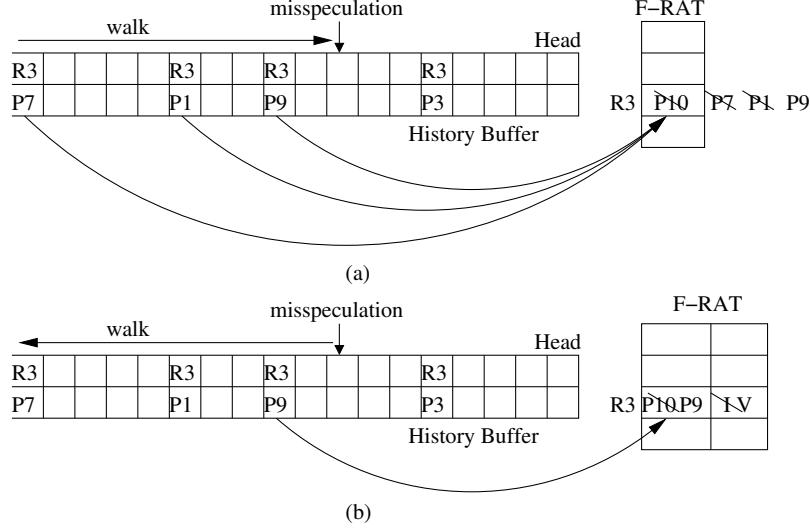

When a misspeculation is detected, the walking process is triggered. Since the walking process operates in the reverse order, the update done by the last instruction is undone first as shown in Figure 2.1(b). The **history buffer** works like a stack and the last pushed content is popped out first. Therefore, the mapping of **R2** is restored to **P4**.

Walking on the **history buffer** eventually restores F-RAT back to the misspeculation point. The time consumed by the walking process is dependent on the number of instructions between the misprediction point and the end of the buffer.

As it can be seen, in case of **history buffer**, walking is done from F-RAT to the misspeculation point. On the other hand, it is also possible to “walk” from R-RAT (Retirement RAT) to the misspeculation point [26, 27]. In this case, the walker needs to have its own RAT, W-RAT(Walker RAT) and copies R-RAT to W-RAT at the beginning of the recovery. Thereafter, the walker goes through the valid instructions from the ROB head to the misspeculation. When an instruction is scanned, its current physical register rather than the previous physical register is used to update W-RAT. At the end, W-RAT has the correct mapping table, which is copied back to F-RAT.

As we have previously mentioned, the overhead of any walking mechanism depends on the number of instruction to scan. These two walking mechanisms which starts from F-RAT or R-RAT are selected due to the misspeculation position. In terms of state, if the misspeculation point is closer to F-RAT, the walker starts from F-RAT. Otherwise, the walker starts from R-RAT.

### 2.1.2 Checkpointing Architectures

An essential task for every recovery mechanism is to restore the future state back to a previous known state. Walking mechanism accomplishes this by undoing the incorrect updates. Checkpointing, on the other hand, can revert the future state back to any point as long as it has a checkpoint of the processor state at that point.

Hwu et al. proposed to use checkpoints for repairing misspeculations [31]. They also described the usage of **history buffer** to do a low overhead recovery. Akkary et al. designed an ROB-free architecture which uses checkpoints to recover from misspeculations [26, 27]. In order to better utilize resources, a branch confidence predictor can be implemented to allocate checkpoints for the branches which are likely to be mispredicted.

Other than a pure checkpointing architecture, many ROB-based architectures also incorporate a checkpoint-based design to optimize the state restoration delay. The MIPS R10000 [32] and Alpha 21264 [33] processors integrated checkpoints to do a fast repair of F-RAT.

Cristal et al. further optimized the checkpointing architecture [34, 35]. In their

technique, a pseudo-ROB was implemented to reduce the number of necessary checkpoints. This pseudo-ROB could retire instructions disregarding their completion status and only assigned a checkpoint if a retired branch was not executed.

Zhou et al. proposed a special mechanism to allocate checkpoints at the misspeculation detection time [36]. Later when the correct F-RAT is restored, the difference between the correct F-RAT and the checkpoint is selected out which is the incorrect mapping updated by the invalid instructions. Additional *MOV* instructions are finally inserted to transfer the correct value to the physical registers mapped by the checkpoint. Since the incorrect mapping is marked ahead, this mechanism does not have state restoration delay.

BranchTap [37] was designed to allocate checkpoints efficiently in a different way. BranchTap would throttle the fetch stage when the number of unresolved, low confidence branches without checkpoints exceeds a threshold. The insight of their mechanism is as follows: the penalty to recover a misspeculation without a checkpoint is higher than the one with a checkpoint. Thus, the number of unresolved branches without checkpoints should be controlled since their recovery would do more damage to the performance. Turbo-ROB [38] was later developed to better recover a misspeculation without a checkpoint. The mechanism packed the ROB storage so that only the necessary mapping information is kept in Turbo-ROB. By doing this, the walking distance became much shorter. As a result, a much quicker recovery is achieved. A

similar approach was also presented in CROB [39].

Other than compressing ROB to shorten the walking distance, Golander et al. designed an approach to reuse the instructions on the walking path [40]. Their mechanism can reuse the results of instructions and the outcome of branches obtained during the first run. They then designed an enhanced checkpoint allocation algorithm [41] which would allocate checkpoints according to dynamic events, such as second-level cache misses and rollback history.

Another cost efficient mechanism, CPROB [42], was proposed to release the physical registers belonging to a checkpoint even before the corresponding branch is resolved. In which case, the physical registers are released much earlier at the cost of a potentially more costly misspeculation recovery.

### 2.1.3 Motivation

Walking is a very general mechanism. Given the contents of **history buffer**, the processor can travel back in time to any point as long as the related record is still in the **history buffer**. The drawback of this approach is that the recovery delay is highly dependent to the walking distance. Furthermore, **history buffer** size restricts the number of speculative instructions. On the other hand, checkpointing based architectures can recover instantly when a misspecified instruction has a checkpoint.

Even if the misspeculated instruction does not have a checkpoint, the recovery can start from a position closer to the misspeculation and therefore have a shorter walking distance. The shortcoming of this technique is the extra overhead in terms of hardware cost and energy consumption. For each checkpoint, a full copy of F-RAT is required and each allocation of the checkpoint consumes extra energy. As a result the mechanism is not efficient.

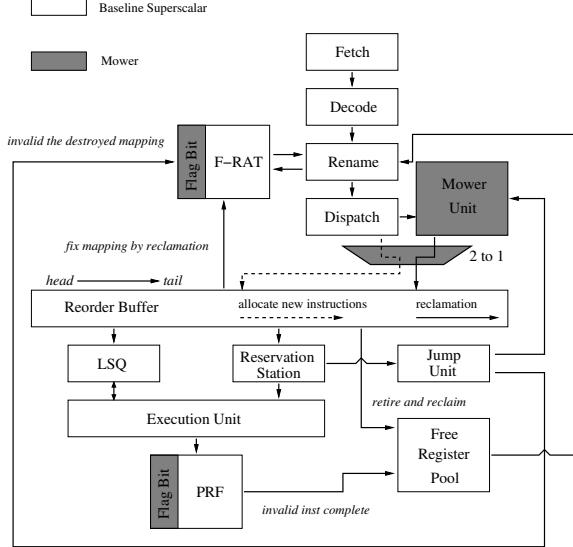

Mower is designed to address these problems in an efficient way. It is a walking-based algorithm so there is no checkpoints need to take, saving energy and design cost. No checkpointing means no instant F-RAT recovery, but that does not mean a longer state restoration delay. Mower has two unique features to curtail the delay. One is that it can rename instructions even before F-RAT is fully restored. The other one is that Mower can fully restore F-RAT in a much shorter distance than a conventional walking algorithm.

F-RAT used in Mower is different in that each logical register's mapping is treated as an individual entity. Therefore, even when the F-RAT is not fully recovered, the renaming continues as long as the instruction's operands have the correct mapping. One simple example is shown in Figure 2.2. The branch is predicted to take the left path so that **R3** and **R4** update F-RAT. When the misprediction of the branch is detected, the mapping in F-RAT updated by invalid instructions are marked to be invalid (**R3** and **R4**). The rest of the map table is still valid. The first newly fetched

instruction reads the mapping of **R1** and **R2** which, in this example, are still valid. In other words, this instruction is allowed to go through the rename stage. The next instruction which reads the mapping of **R3** is stalled as the mapping is invalid at that point.

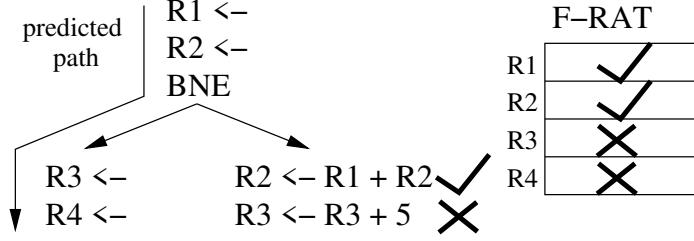

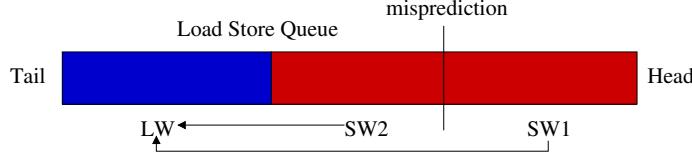

**Figure 2.2:** Renaming with a not fully correct F-RAT

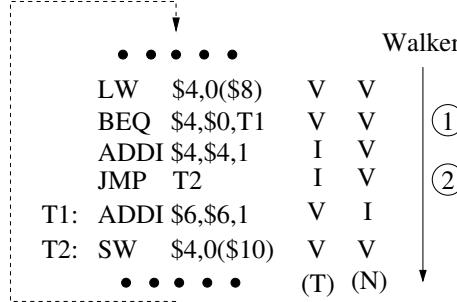

With the knowledge of F-RAT changes in Mower, it becomes much easier to explain the walking process that is employed in Mower. A conventional walking process is shown in Figure 2.3(a). For simplicity, only **R3**'s updates are shown in the figure. When a misspeculation is detected, the walking process will undo the updates in reverse program order. Whenever an **R3**'s entry is encountered, F-RAT is changed. The correct mapping of **R3** is not determined until the walking process is finished since the walker has no knowledge which logical register will be changed next. At the end, F-RAT is fully recovered.

It is easy for Mower to have a short-cut because Mower can identify the valid mapping at a finer grain. Figure 2.3(b) shows the walking process of Mower in which the walker follows the program order starting from the misspeculation. When **R3** is encountered

**Figure 2.3:** The different walking direction in Mower

the first time, Mower checks F-RAT and finds that it is an invalid mapping. Hence, Mower updates **R3** with **P9** and sets the mapping to valid. Because the mapping becomes valid, it is not changed any more for the rest of the walking process. The insight is, if the walking process follows the program order, the first entry of the invalid mapping register contains the correct mapping, since this entry holds the update made before the misspeculation.

If we consider both of the algorithms described above, it becomes clear that Mower can recover the register mapping much faster because each mapping has its own valid bit. Besides, when a single register mapping is recovered, it helps to rename the instruction which reads this logical register and everything is done without a fully recovered F-RAT.

## 2.2 Control Dependence Tracking

When a misspeculation is detected in Mower, invalid register mappings have to be identified immediately since the walker needs the validation information to recover. Thus in Mower, every branch is given a special tag. When the branch is mispredicted, the branch tag is broadcast and the affected register mappings are marked to be invalid. In this section, the related structures are thoroughly explained.

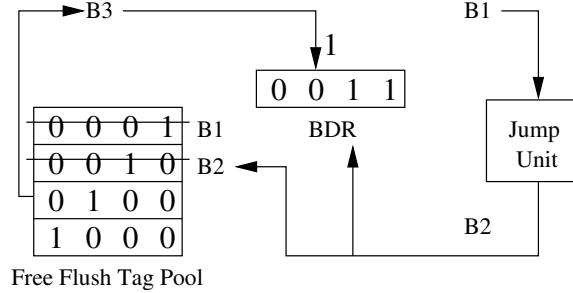

### 2.2.1 Branch Renaming

For every decoded branch, a special tag, branch flush tag, is allocated. A normal rename policy such as the register renaming algorithm does not fit well to rename branches. This is because, a single instruction may depend on multiple unresolved branches and this one to N mapping does not exist in register renaming.

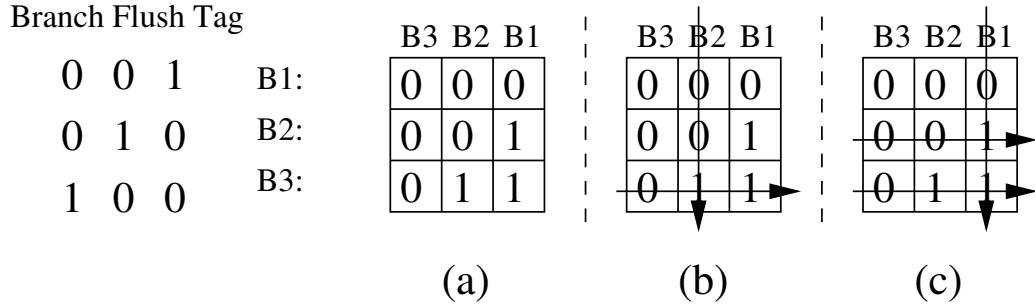

McIlvaine et al. had a patent [25] to rename branches and their approach can solve this one to N dependence tracking effectively. The branch flush tag is a bit vector which has only one bit set high. Therefore, the width of the vector determines the total number of flush tags. For example, if the vector is 4-bit wide, the complete tag set is 1000, 0100, 0010, 0001. In other words, four branches at most can be renamed.

When a branch is executed, its flush tag is not needed any more so the tag is released and the tag can be allocated to a new branch. In summary, the branch flush tag's width decides the number of unresolved branches.

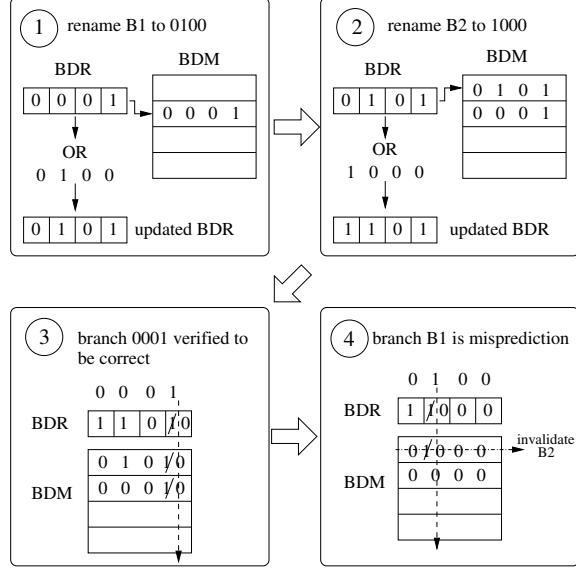

### 2.2.2 Disambiguating the Branch Ordering

In general, there are multiple unresolved branches in the pipeline and it is possible that more than one branch is mispredicted. Consequently, when a recovery process is underway, another misprediction can be detected. At that moment, the branch ordering is very important. An older misprediction should overwrite the current recovery process and a younger misprediction should be ignored. Normally, a superscalar processor would compare the sequence number of the branches to decide the branch age [43]. Instead, each branch instruction in Mower has a dedicated tag. This approach enables the use of a control dependence matrix to implement proper branch ordering.

Such dependency matrices were first proposed to replace the CAM-based reservation stations [44, 45]. Each row in the matrix represents an individual instruction and each column represents a dependent component. Whenever all the dependencies are cleared in one row, the corresponding instruction is ready to issue.

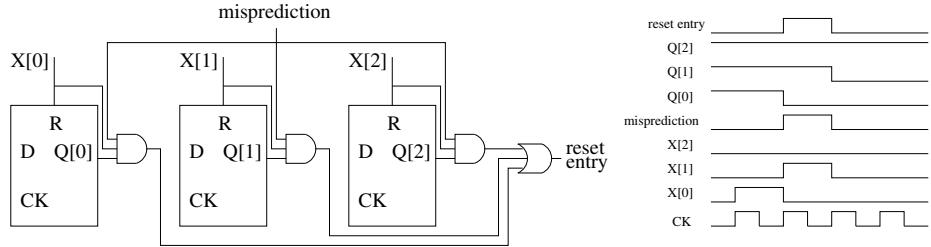

In Mower, a **Branch Dependence Matrix** (BDM) is used to identify the ordering of

the branches. Figure 2.4(a) shows a simple example in which there are three branches renamed to “001”, “010” and “100”. The branch dependence matrix shown on the right side is a 3X3 matrix. Each row represents a branch and the values in the row represent the dependencies of this branch. If the value is high that means the branch is dependent on another branch which is on that column. For example, branch **B2** is dependent on **B1** as **B2** is fetched after **B1**. In the matrix, the row of **B2** is “001” and the corresponding column is **B1**. Branch **B3** is dependent on both **B1** and **B2**, its row then is “011”.

**Figure 2.4:** The branch dependence matrix

When a branch instruction is mispredicted, its flush tag is broadcast to invalidate those branches which were fetched afterwards. For example, in Figure 2.4(b), branch **B2** is mispredicted and its column is invalidated. Wherever the entry is set high, the corresponding row will be invalidated. In this example, branch **B3** is invalidated. When **B1** is mispredicted, both **B2** and **B3** are invalidated (Figure 2.4(c)). Only a valid branch instruction can trigger a misprediction recovery.

### 2.2.3 Tracking Affected F-RAT entries

The dependence matrix can also be used to track the register mappings. As we have discussed before, Mower treats each logical register mapping as an individual entity. When a misprediction is detected, the mapping which is updated after the misprediction is invalidated. This is accomplished by using another dependence matrix.

|     | B1 | B2 | B3 | B4 | ..... | Bn | Valid |

|-----|----|----|----|----|-------|----|-------|

| R0  | 0  | 0  | 0  | 0  | ..... | 0  | 1     |

| R1  | 1  | 0  | 0  | 0  | ..... | 0  | 1     |

| R2  | 1  | 1  | 0  | 0  | ..... | 0  | 1     |

| R3  | 0  | 0  | 0  | 0  | ..... | 0  | 1     |

| ⋮   | ⋮  | ⋮  | ⋮  | ⋮  | ⋮     | ⋮  | ⋮     |

| R31 | ⋮  | ⋮  | ⋮  | ⋮  | ⋮     | ⋮  | 1     |

**Figure 2.5:** The mapping dependence matrix

Figure 2.5 shows a **Mapping Dependence Matrix** (MDM) which has 32 rows and  $n$  columns. Each row represents a logical register's dependencies and each column represents an unresolved branch. Thus at most  $n$  unresolved branches are included. When a logical register is renamed, all unresolved branch tags are written into the corresponding register row and the row is also marked as valid. Whenever a misprediction is detected, the corresponding column is broadcast and any row which has the dependence bit set is invalidated. In Figure 2.5, the mapping of **R2** is invalidated when branch **B2** is mispredicted.

## 2.3 A Reverse Walking Procedure

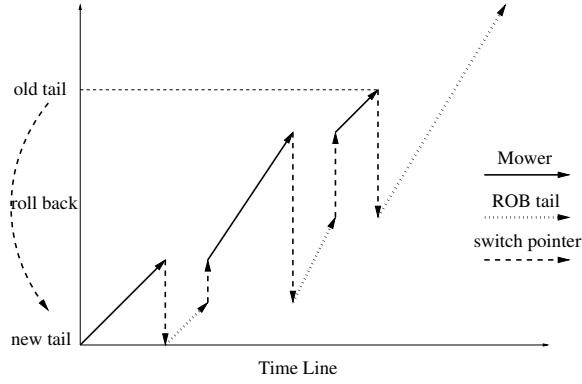

The walker in Mower has two major tasks during the recovery procedure. First, it scans the history buffer to restore F-RAT and second, it eliminates the stale instructions and reclaims the occupied resources. The walking process starts from the misprediction and moves towards the ROB tail. This walking direction is opposite to the previous walking mechanisms and it accelerates the F-RAT recovery.

### 2.3.1 Recovering F-RAT in a gradual manner

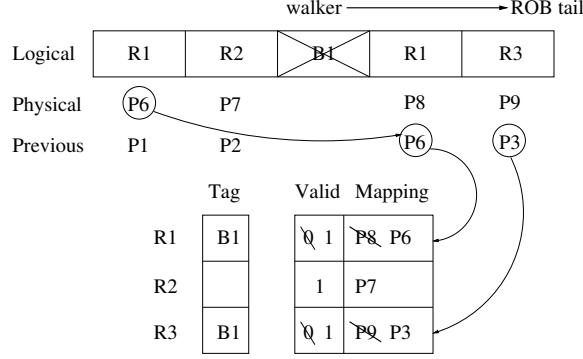

Once a misprediction is detected, MDM is searched and the register mappings which were modified after the misprediction are marked invalid. Figure 2.6 illustrates this recovery procedure. The instructions are placed in program order from left to right. The register mappings (from logical registers to physical registers) are shown in the first two rows. The row of “Previous” contains the previous physical register identity of the logical registers. For example, **R1** is mapped to **P6** in the first instruction and then mapped to **P8** in the 4th instruction. The previous register identity **P6** is kept in the 4th instruction. This approach works similar to a history buffer.

The register mappings of **R1** and **R3** are modified after **B1**, thus these two mappings

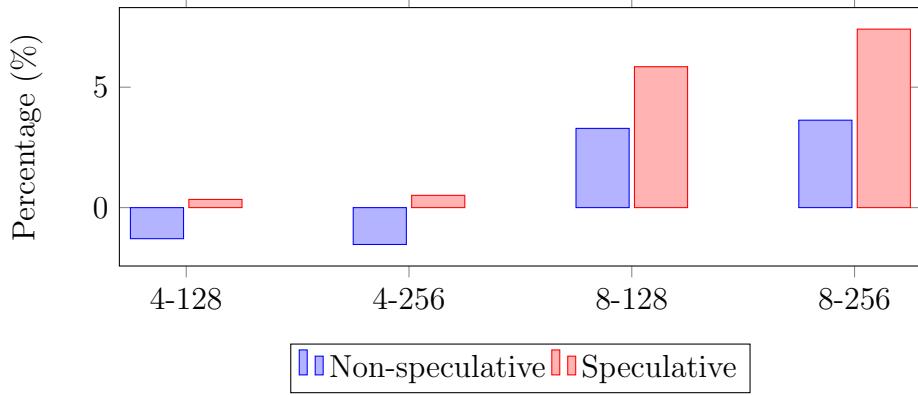

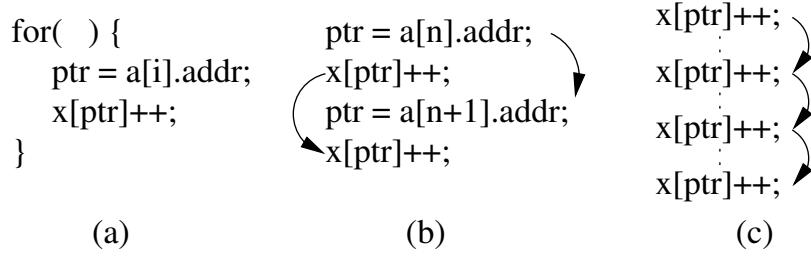

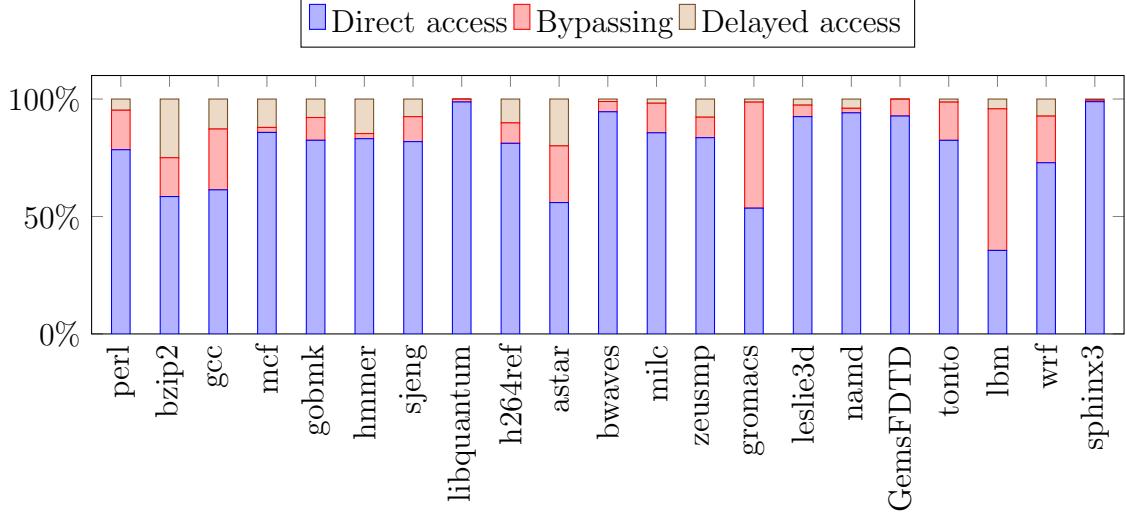

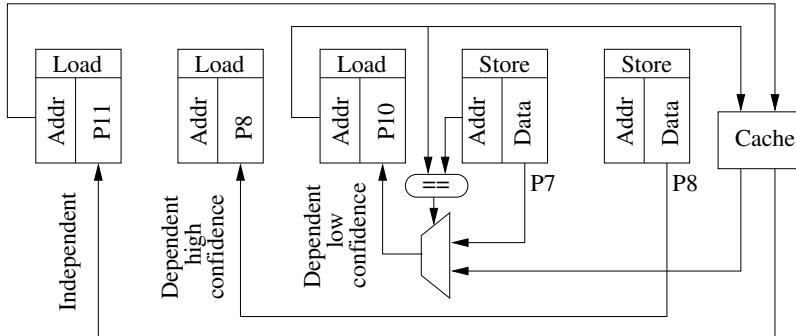

**Figure 2.6:** Recovering F-RAT by walking from the misprediction to ROB tail