FINE-GRAIN STATE PROCESSORS

By

PENG ZHOU

A DISSERTATION

Submitted in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

(Computer Science)

MICHIGAN TECHNOLOGICAL UNIVERSITY

2009

Copyright © Peng Zhou 2009

This dissertation, "Fine-grain State Processors," is hereby approved in partial fulfillment of the requirements for the degree of DOCTOR OF PHILOSOPHY in the field of Computer Science.

DEPARTMENT:

Computer Science

Signatures:

Dissertation Advisor \_\_\_\_\_

Dr. Soner Önder

Committee \_\_\_\_\_

Dr. Steven M. Carr

\_\_\_\_\_

Dr. David A. Poplawski

\_\_\_\_\_

Dr. Brian T. Davis

Department Chair \_\_\_\_\_

Dr. Linda M. Ott

Date \_\_\_\_\_

*To My Parents and My Wife*

## Acknowledgement

First and foremost, I would like to thank my advisor Dr. Soner Önder, for his support, guidance, and encouragement in the Ph.D program. He showed me the way to approach research problems and taught me how to express my ideas. I am deeply impressed by his inspiring and encouraging way to guide me to a deeper understanding of knowledge. I am grateful for his advise and comments in this dissertation.

I also would like to thank the rest of my thesis committee: Dr. Steve Carr, Dr. David Poplawski, and Dr. Brian Davis, for their kind help and valuable comments on this work. Thanks also go to Dr. Zhenlin Wang from our research group, who gave me the suggestion and helped me on the career selection.

I really appreciate my friends and colleagues in school, who had fun with me and gave me the help in a place far away from home. I really enjoyed the life with them in the beautiful Keweenaw Peninsula.

Last but not least, I wish to thank my parents and my sister, for their continued support and encouragement. I am also very grateful to my wife Xiaodi, for her love and patience during my Ph.D period.

## Abstract

Proper manipulation of processor state is crucial for high performance speculative superscalar processors. This dissertation presents a new state paradigm. In this paradigm, the processor is aware of the in-order, speculative and architectural states on an individual data location basis, rather than with respect to a particular point in the program's execution. We refer to the traditional processors which adopt a lump-sum approach with respect to the processor state as *Coarse-grain State Processors (CSP)*, and those which can classify individual data locations belonging to a particular state as *Fine-grain State Processors (FSP)*.

Fine-grain State Processors break the atomic state set into finer granularity at the individual value level. As a result, they can utilize correct values upon a mis-speculation. Furthermore, they can continue execution with a partially correct state and still maintain correct program semantics. Performing the state recovery without stopping the execution of future instructions potentially can hide the latency of the recovery process, resulting in zero-penalty speculation under ideal conditions.

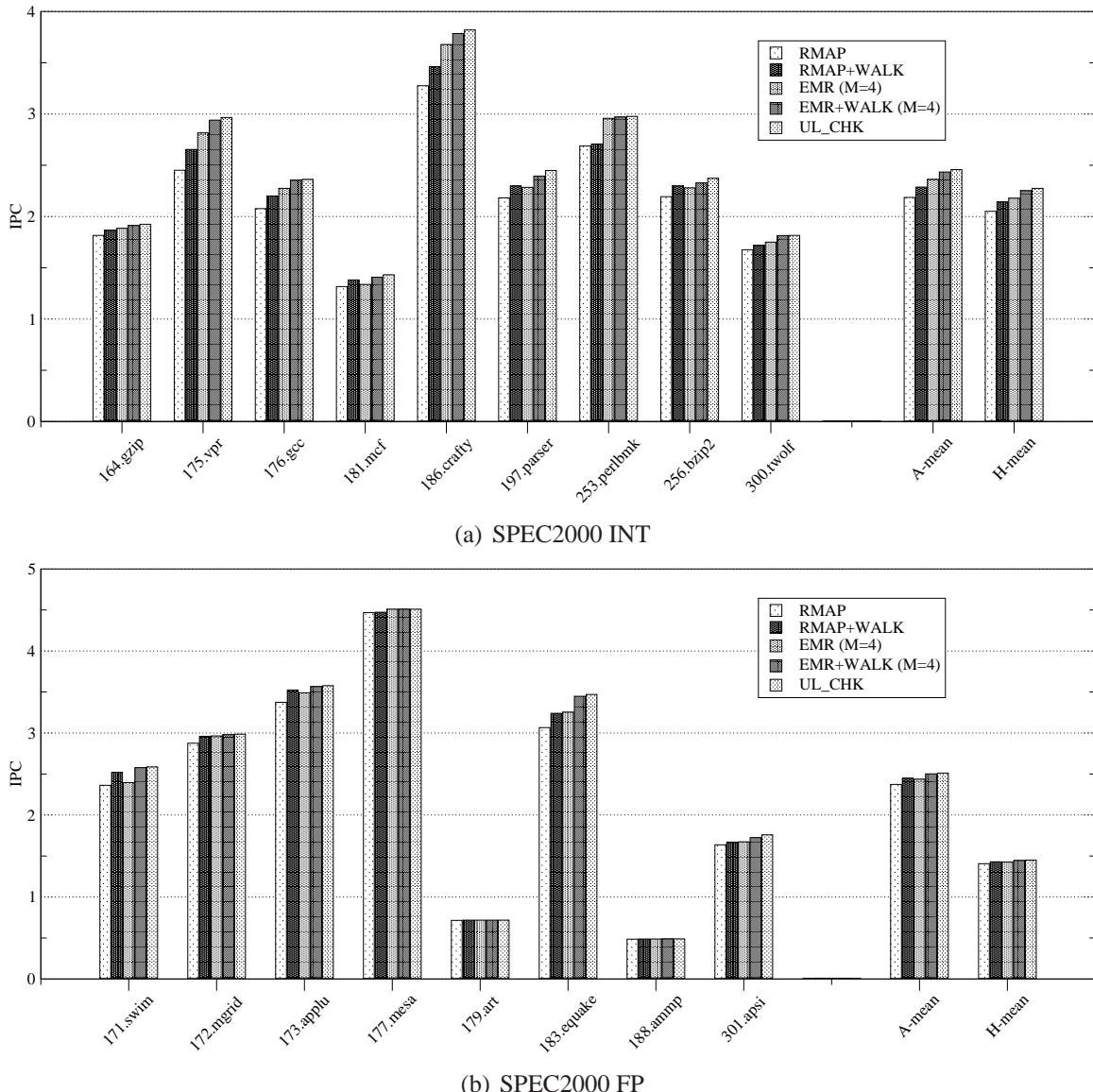

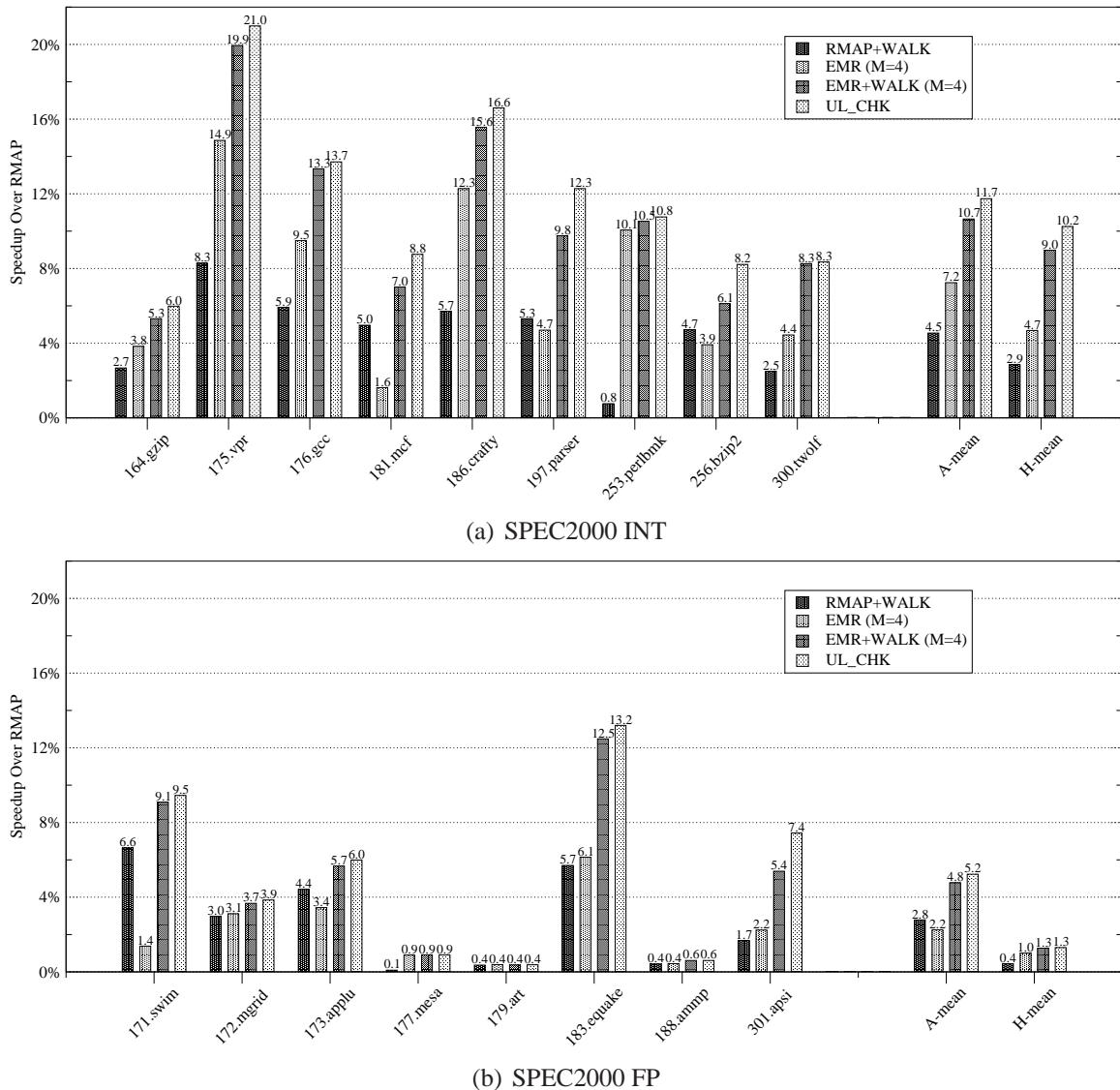

This dissertation also presents a taxonomy of FSP. The taxonomy categorizes existing fine-grain state handling techniques and outlines the design space of future FSP designs. Based on the developed general framework, the dissertation explores applications of FSP on sophisticated uni-processor as well as multi-core/multi-threaded organizations. Two detailed FSP models are evaluated, *EMR* and *FSG-RA*, regarding control speculation and value speculation, respectively. In both models, the FSP technique handles processor states more efficiently and obtains much higher performance than traditional mechanisms. For example, EMR achieves an average of 9.0% and up to 19.9% better performance than traditional course grain state handling on the SPEC CINT2000 benchmark suite, while FSG-RA obtains an average of 38.9% and up to 160.0% better performance than a comparably equipped CSP processor on the SPEC CFP2000 benchmark suite.

# Contents

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>Acknowledgement</b>                                             | <b>iv</b> |

| <b>Abstract</b>                                                    | <b>1</b>  |

| <b>List of Figures</b>                                             | <b>8</b>  |

| <b>List of Tables</b>                                              | <b>9</b>  |

| <b>1 Introduction</b>                                              | <b>10</b> |

| 1.1 Motivation . . . . .                                           | 10        |

| 1.2 Research Goals . . . . .                                       | 16        |

| 1.3 Dissertation Organization . . . . .                            | 20        |

| <b>2 Background</b>                                                | <b>21</b> |

| 2.1 Out-of-order Execution and Speculative Execution . . . . .     | 21        |

| 2.2 Processor States . . . . .                                     | 24        |

| 2.3 State Maintenance and Recovery . . . . .                       | 26        |

| 2.3.1 State re-constructing . . . . .                              | 26        |

| 2.3.2 Checkpointing . . . . .                                      | 33        |

| 2.4 Register Renaming and State Maintenance and Recovery . . . . . | 37        |

| 2.4.1 RAM-structured MAP . . . . .                                 | 39        |

| 2.4.2 CAM-structured MAP . . . . .                                 | 43        |

|                                                              |           |

|--------------------------------------------------------------|-----------|

|                                                              | 3         |

| 2.5 Summary of Background . . . . .                          | 46        |

| <b>3 Simulation and Experimental Setup</b>                   | <b>47</b> |

| 3.1 Simulation Tools . . . . .                               | 47        |

| 3.2 Benchmark Suites and Environment . . . . .               | 49        |

| <b>4 Taxonomy of Fine-grain State Processors</b>             | <b>53</b> |

| 4.1 Roll-back + Reuse Results . . . . .                      | 54        |

| 4.1.1 Squash and Re-fetch Instructions . . . . .             | 54        |

| 4.1.2 Re-issue Fetched Instructions . . . . .                | 56        |

| 4.2 Continue Without Roll-back . . . . .                     | 57        |

| 4.2.1 Sequential Recovery . . . . .                          | 57        |

| 4.2.2 Parallel Recovery . . . . .                            | 58        |

| 4.3 Summary of Taxonomy . . . . .                            | 59        |

| <b>5 Fine-grain State Processor</b>                          | <b>60</b> |

| 5.1 A General FSP Framework . . . . .                        | 60        |

| 5.2 Coarse-grain State VS. Fine-grain State . . . . .        | 65        |

| 5.3 Summary of FSP's Framework . . . . .                     | 68        |

| <b>6 Eager branch Mis-prediction Recovery</b>                | <b>69</b> |

| 6.1 Introduction . . . . .                                   | 69        |

| 6.2 Design Space . . . . .                                   | 71        |

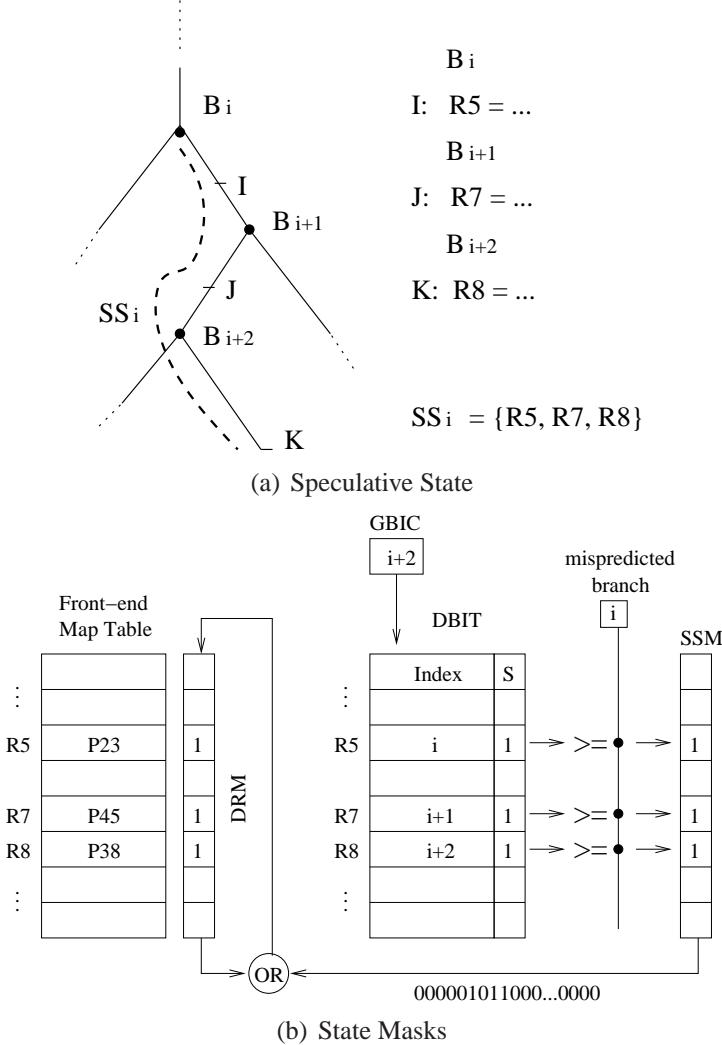

| 6.2.1 Identifying Speculative State . . . . .                | 71        |

| 6.2.2 Handling Multiple Mis-predictions . . . . .            | 74        |

| 6.2.3 Blocking and Shelving Dependent Instructions . . . . . | 79        |

|          |                                                   |           |

|----------|---------------------------------------------------|-----------|

| 6.2.4    | Correcting Incorrect Speculative State            | 80        |

| 6.2.5    | Parallelism in Recovery                           | 82        |

| 6.3      | Optimization                                      | 83        |

| 6.4      | Experimental Evaluation                           | 85        |

| 6.4.1    | Experimental Methodology                          | 85        |

| 6.4.2    | Performance Results                               | 86        |

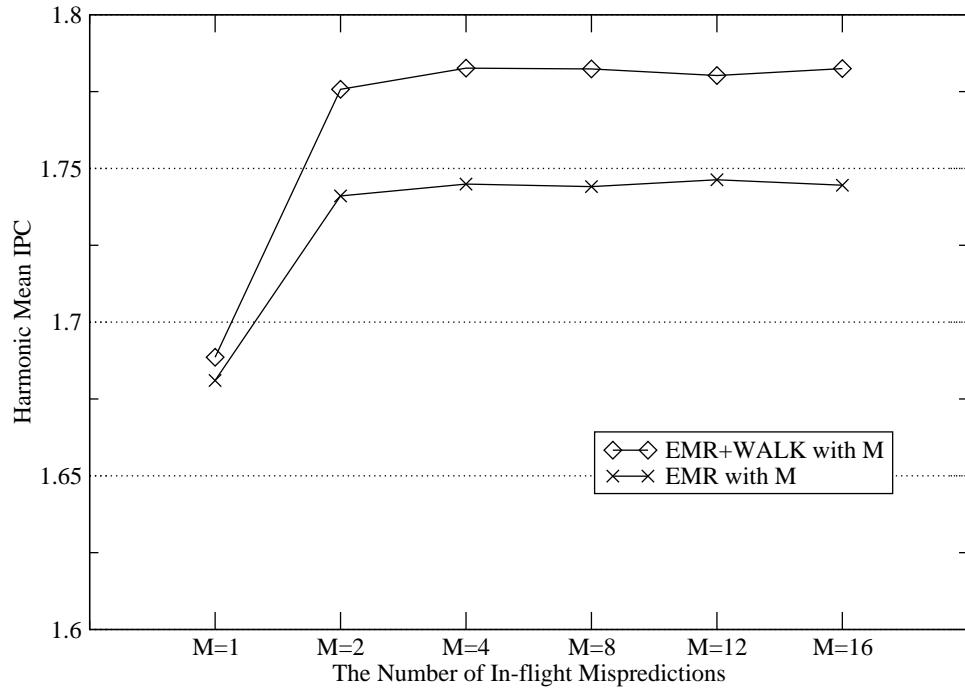

| 6.4.3    | Mis-predictions-under-Mis-predictions             | 91        |

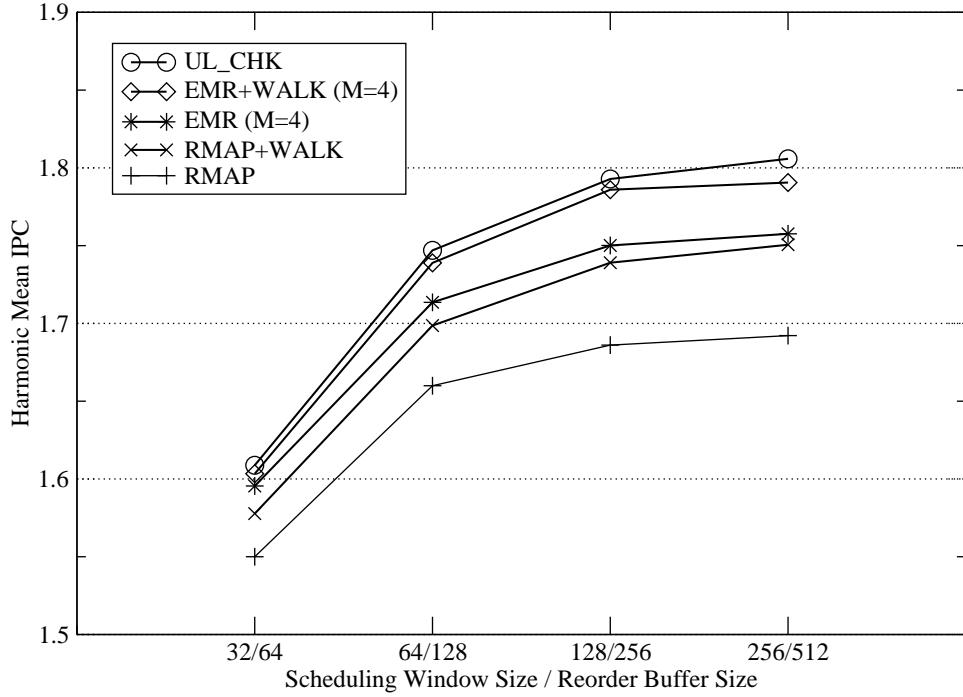

| 6.4.4    | Towards a Large Instruction Window                | 93        |

| 6.5      | Related Work                                      | 94        |

| 6.6      | Summary of EMR                                    | 96        |

| <b>7</b> | <b>Fine-grain State Guided Runahead Execution</b> | <b>98</b> |

| 7.1      | Introduction                                      | 98        |

| 7.2      | SMT FSG-RA                                        | 101       |

| 7.3      | State Maintenance                                 | 105       |

| 7.4      | Termination of Runahead Mode                      | 108       |

| 7.5      | Thread Memory Dependencies                        | 111       |

| 7.6      | Detecting Memory Order Violations                 | 114       |

| 7.7      | Re-Executing Only Dependent Instructions          | 117       |

| 7.7.1    | Handling the Register State                       | 119       |

| 7.7.2    | Handling the Memory State                         | 120       |

| 7.8      | Experimental Evaluation                           | 121       |

|          |                                |            |

|----------|--------------------------------|------------|

| 7.8.1    | Performance Results            | 122        |

| 7.8.2    | Efficiency of FSG-RA           | 125        |

| 7.8.3    | Effect of Branches             | 128        |

| 7.9      | Related Work                   | 130        |

| 7.10     | Summary of FSG-RA              | 132        |

| <b>8</b> | <b>Conclusion</b>              | <b>133</b> |

| 8.1      | Dissertation Contributions     | 134        |

| 8.2      | Future Directions for Research | 136        |

# List of Figures

|      |                                                                                            |    |

|------|--------------------------------------------------------------------------------------------|----|

| 1.1  | Mis-speculation and its effect on state . . . . .                                          | 12 |

| 1.2  | Percentage of Speculative State upon Mis-predictions . . . . .                             | 14 |

| 1.3  | Distribution of References to Damaged/Non-Damaged Registers upon Mis-predictions . . . . . | 15 |

| 2.1  | Exception and Mis-speculation Boundaries . . . . .                                         | 22 |

| 2.2  | In-order, Speculative and Architectural States upon Speculation . . . . .                  | 25 |

| 2.3  | Reorder Buffer . . . . .                                                                   | 28 |

| 2.4  | History Buffer . . . . .                                                                   | 30 |

| 2.5  | Future File . . . . .                                                                      | 32 |

| 2.6  | Checkpointing Maintenance and Recovery Scheme . . . . .                                    | 33 |

| 2.7  | Logical Space of Memory by Backward Difference . . . . .                                   | 36 |

| 2.8  | Logical Space of Memory by Forward Difference . . . . .                                    | 37 |

| 2.9  | RAM-structured Map Table . . . . .                                                         | 39 |

| 2.10 | Checkpoint Stack in MIPS R10000 . . . . .                                                  | 41 |

| 2.11 | State Re-constructing in Pentium IV . . . . .                                              | 42 |

|      |                                                                      |     |

|------|----------------------------------------------------------------------|-----|

| 2.12 | CAM-structured Map Table . . . . .                                   | 44  |

| 2.13 | Per-Instruction Boundary State Recovery in Alpha 21264 . . . . .     | 45  |

| 3.1  | Fast Functional Simulator . . . . .                                  | 48  |

| 3.2  | 5-Stage Pipeline Simulator . . . . .                                 | 48  |

| 3.3  | Superscalar Simulator . . . . .                                      | 49  |

| 4.1  | Taxonomy of Fine-grain State Processors . . . . .                    | 53  |

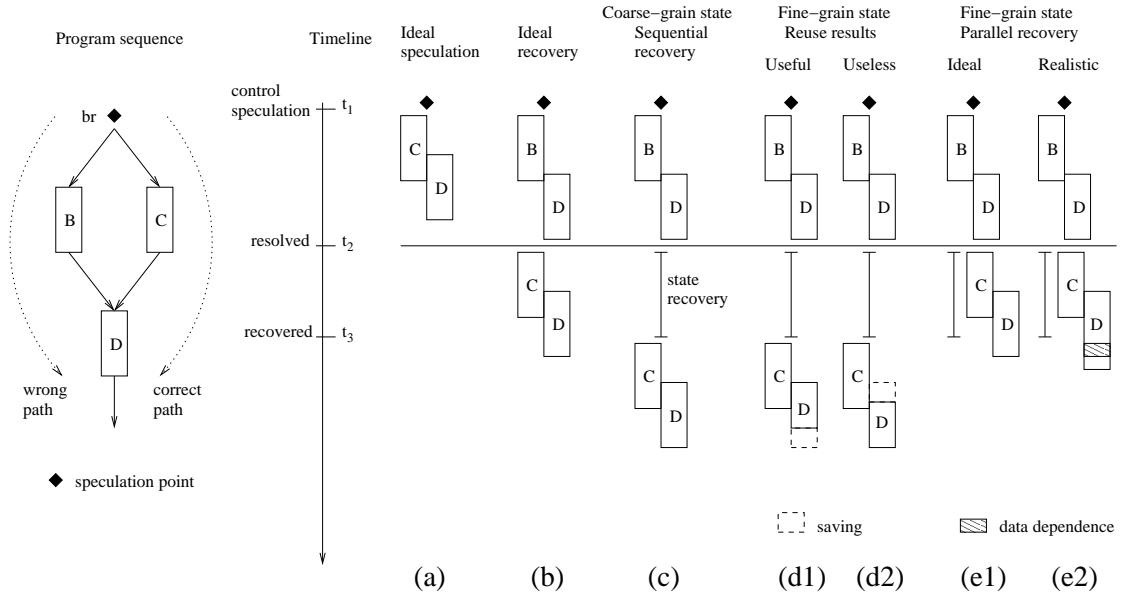

| 5.1  | Control Speculation . . . . .                                        | 65  |

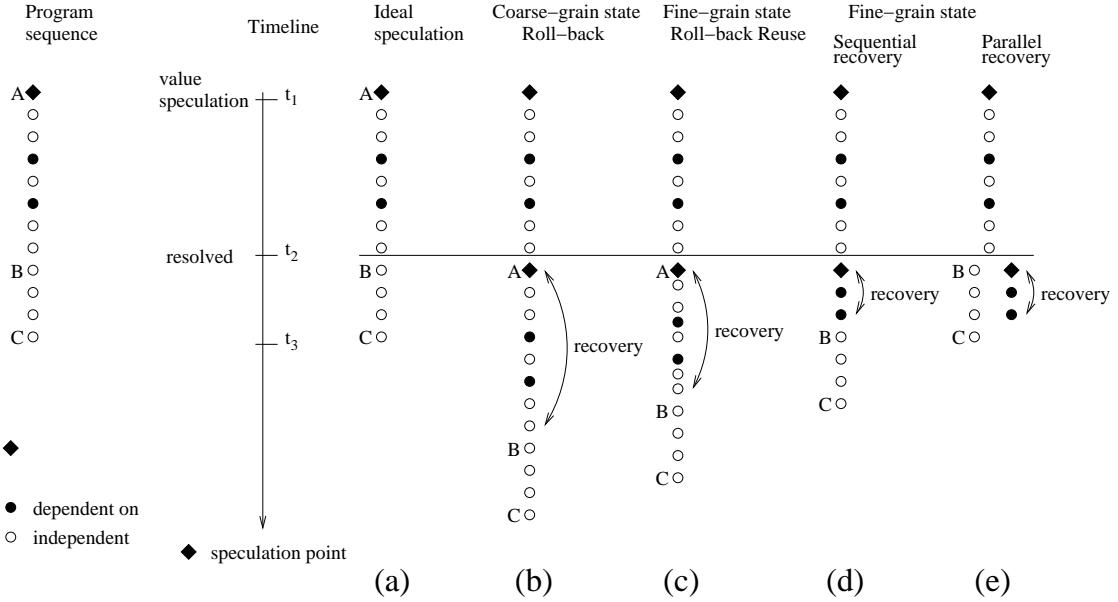

| 5.2  | Value Speculation . . . . .                                          | 67  |

| 6.1  | Identifying Speculative State . . . . .                              | 72  |

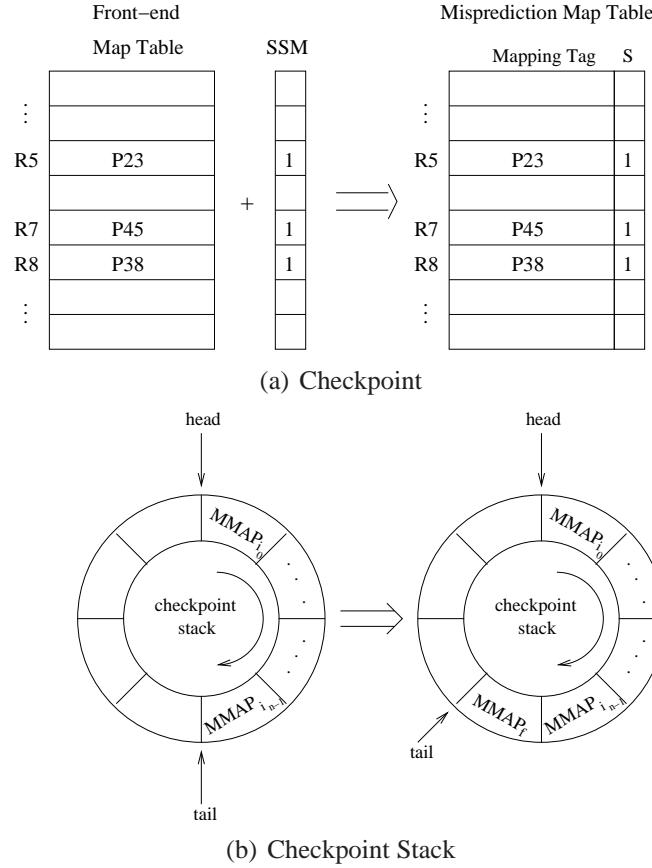

| 6.2  | Checkpointing to Handle Multiple Mis-predictions . . . . .           | 76  |

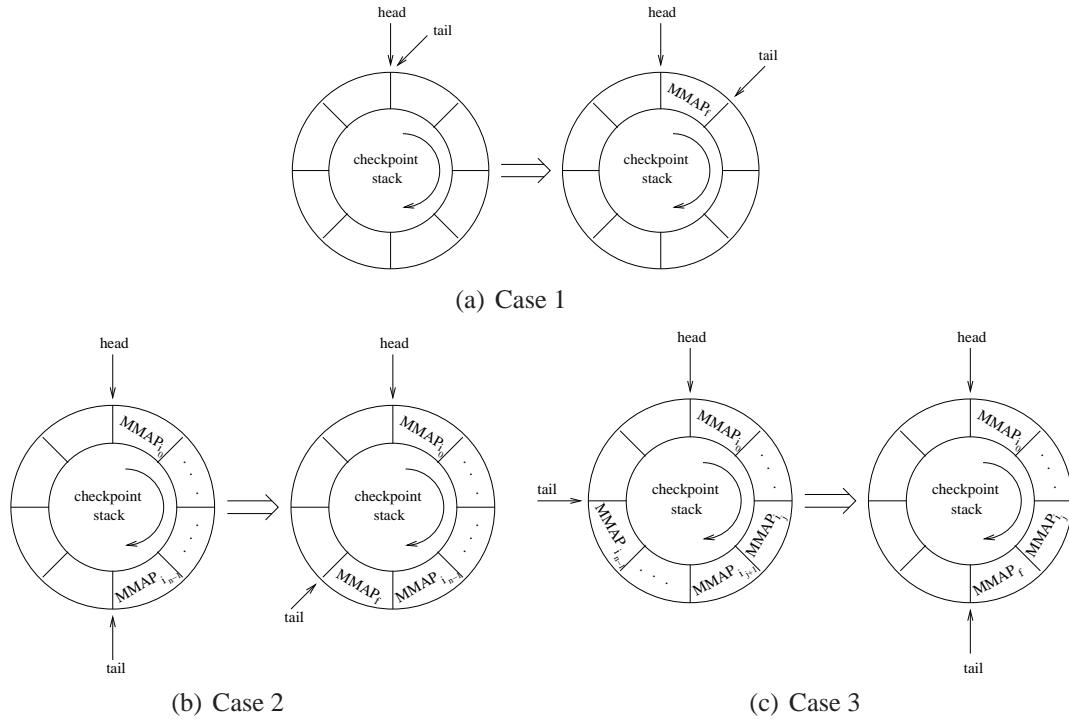

| 6.3  | Three Cases of Multiple Mis-predictions . . . . .                    | 77  |

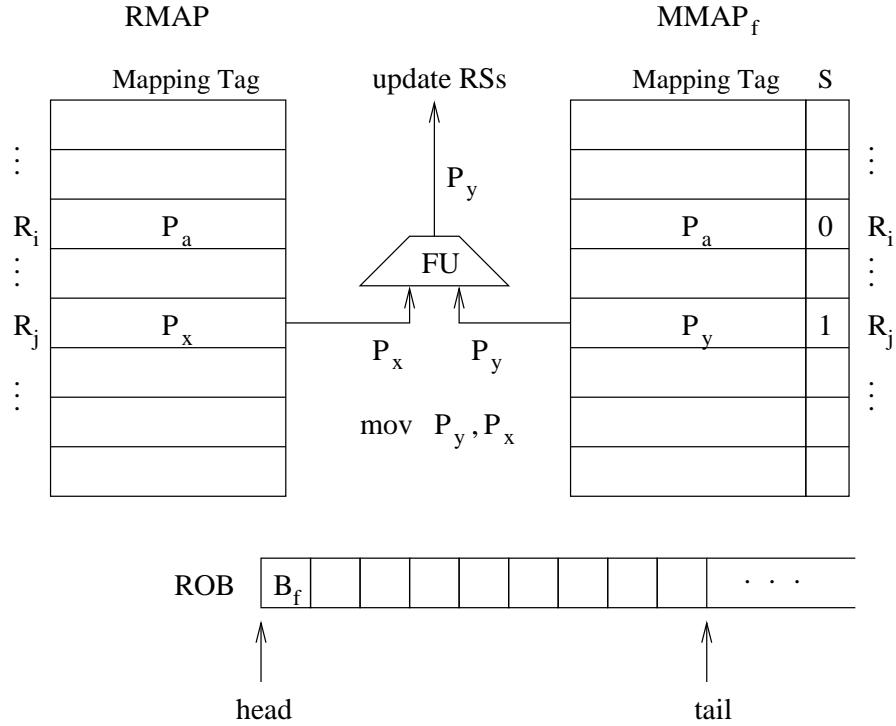

| 6.4  | Restoring Speculative State . . . . .                                | 81  |

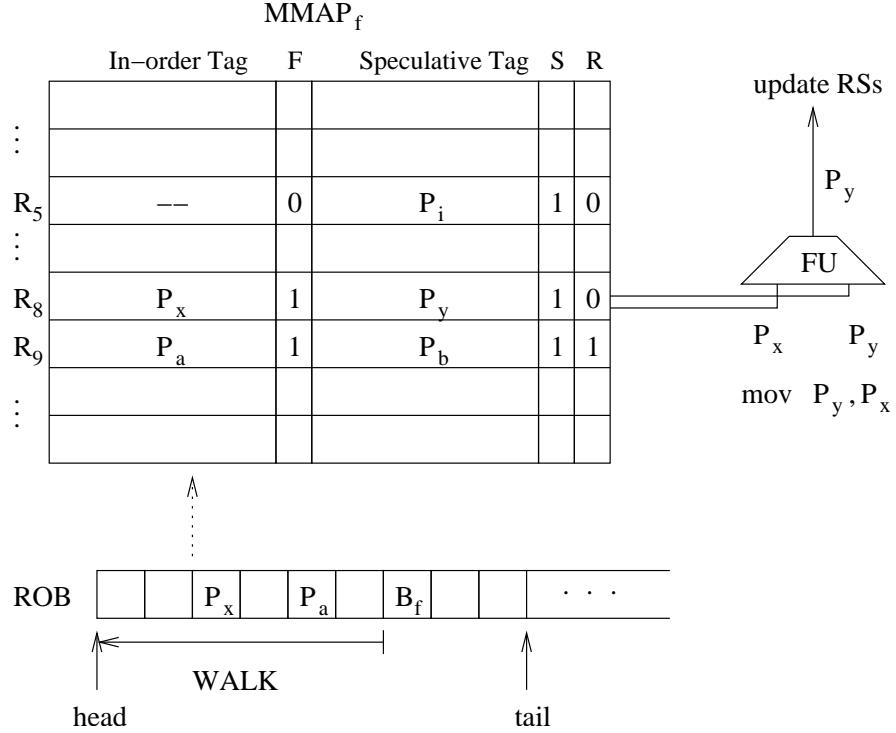

| 6.5  | EMR+WALK . . . . .                                                   | 84  |

| 6.6  | Performance of five models . . . . .                                 | 88  |

| 6.7  | Speedup of RMAP+WALK, EMR/+WALK (M=4) and UL_CHK over RMAP . . . . . | 89  |

| 6.8  | Performance of EMR/+WALK with Different M . . . . .                  | 92  |

| 6.9  | Performance of 5 Models with Different SW/ROB sizes . . . . .        | 94  |

| 7.1  | Value Speculation . . . . .                                          | 100 |

| 7.2  | SMT FSG-RA machine model . . . . .                                   | 102 |

|      |                                               |     |

|------|-----------------------------------------------|-----|

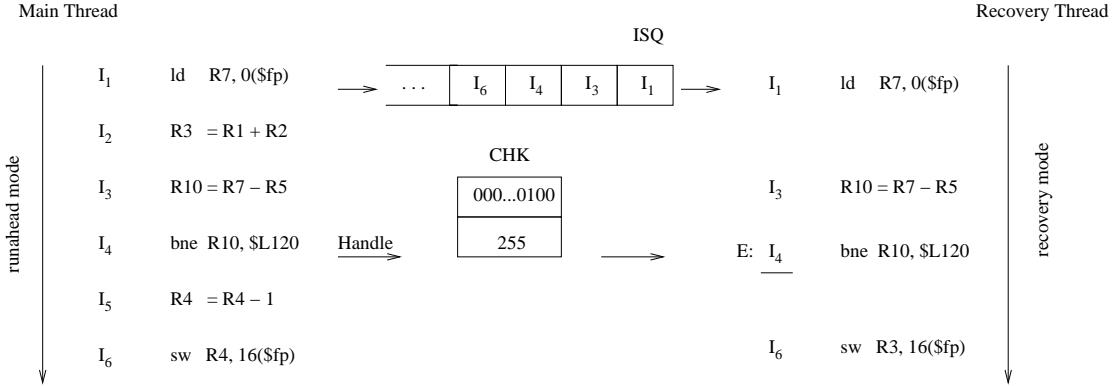

| 7.3  | Fine grain state recovery                     | 107 |

| 7.4  | Memory Ordering in FSG-RA                     | 113 |

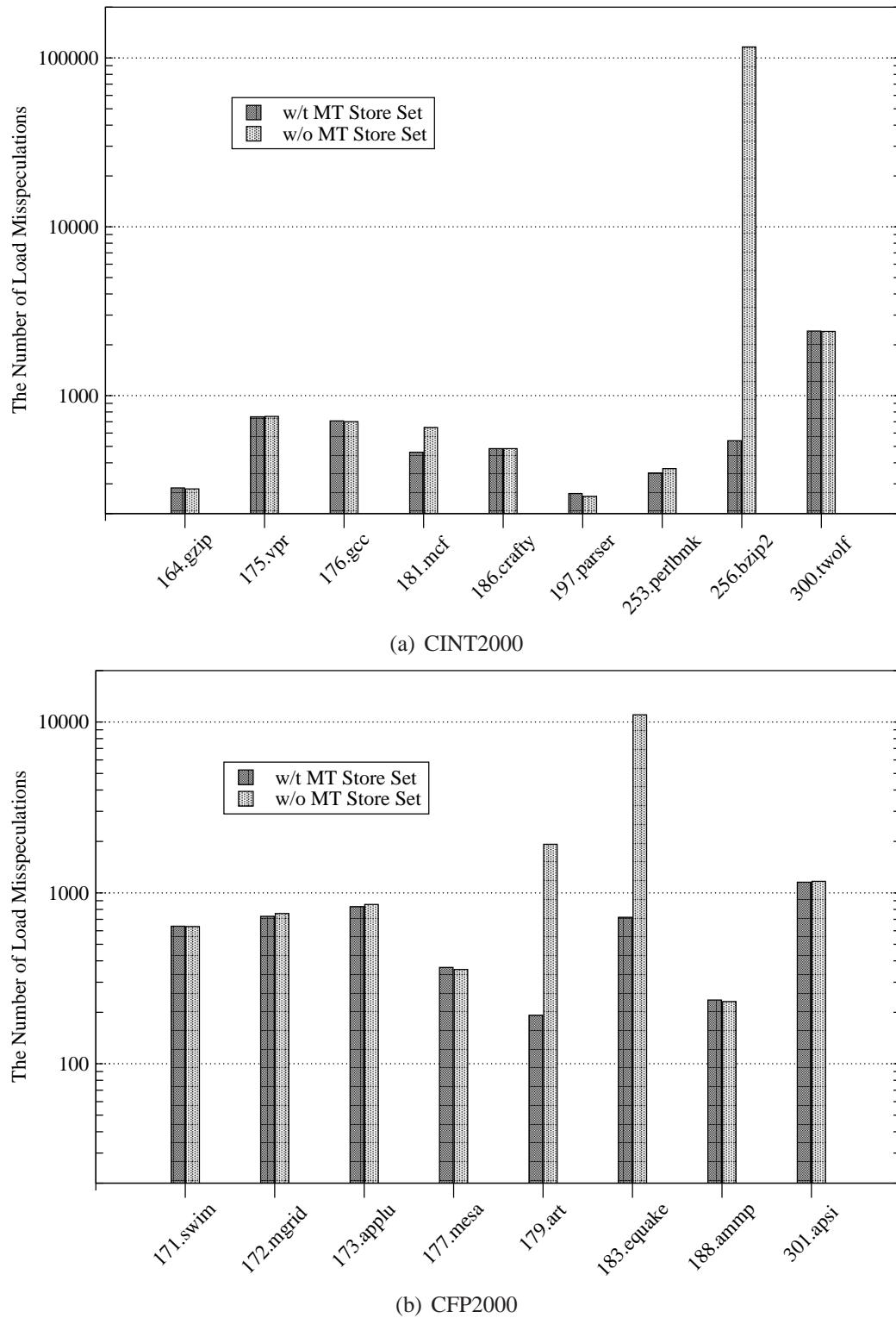

| 7.5  | Mis-speculations Enhanced Store Set Algorithm | 116 |

| 7.6  | Example of FSG-RA-dep                         | 118 |

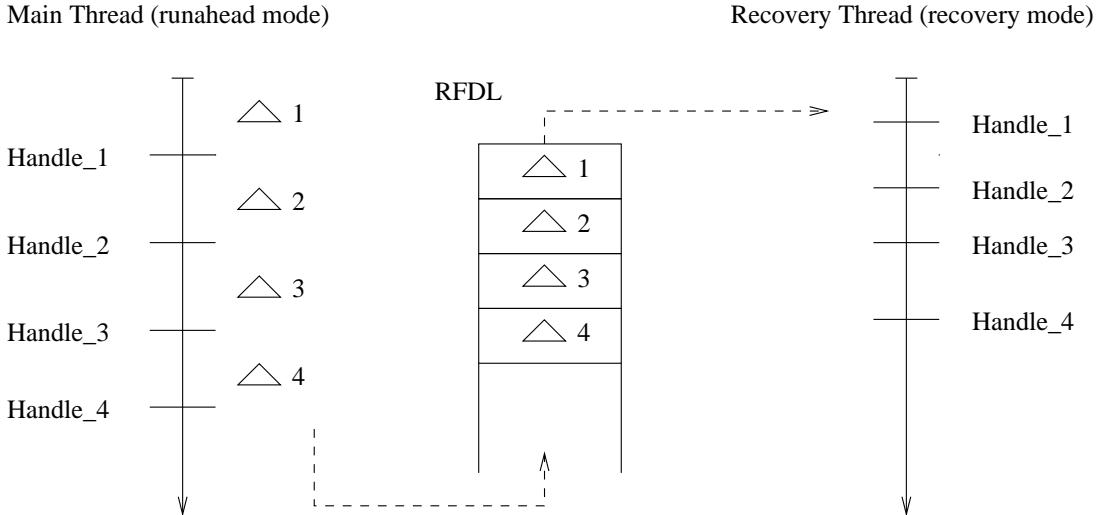

| 7.7  | Multiple Handles                              | 119 |

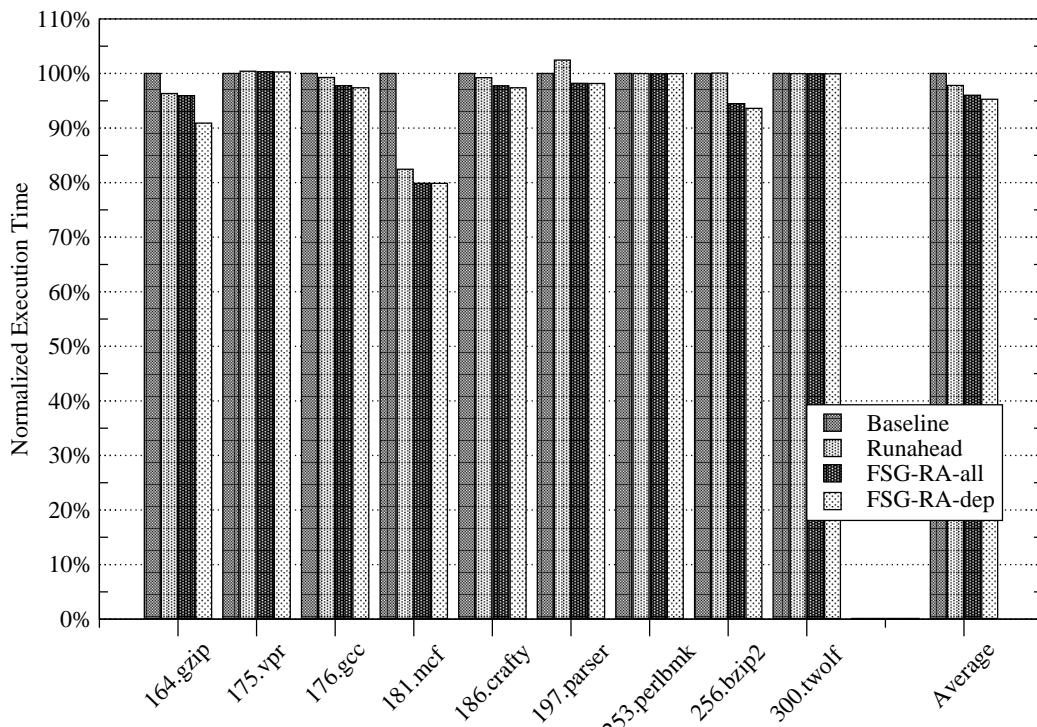

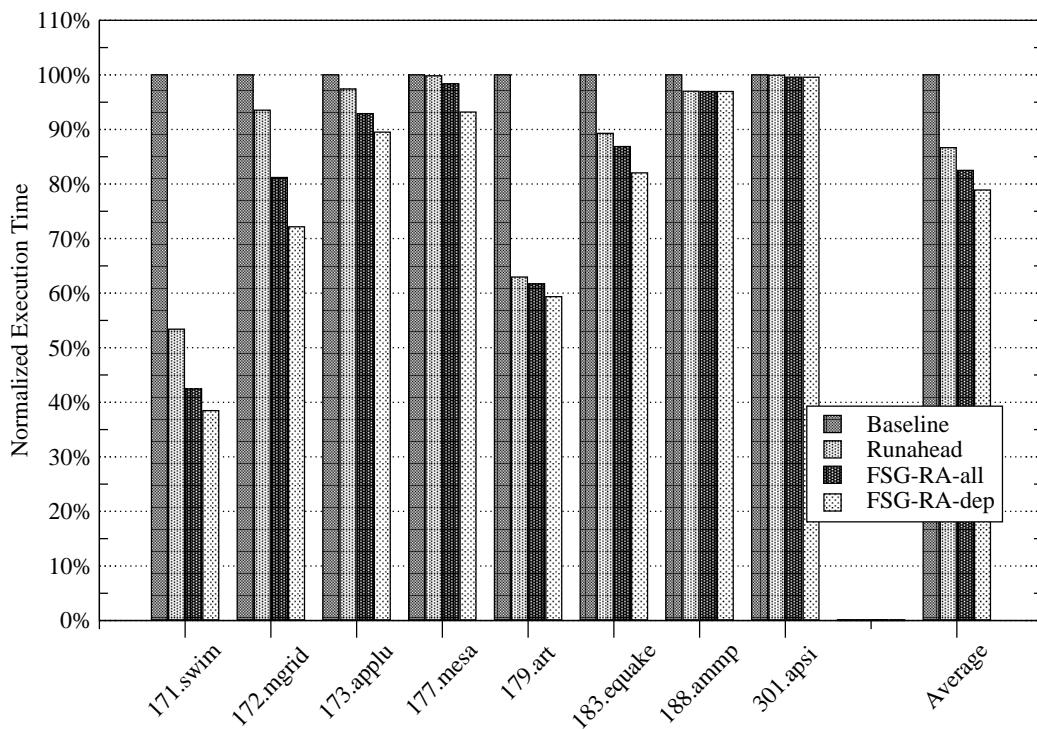

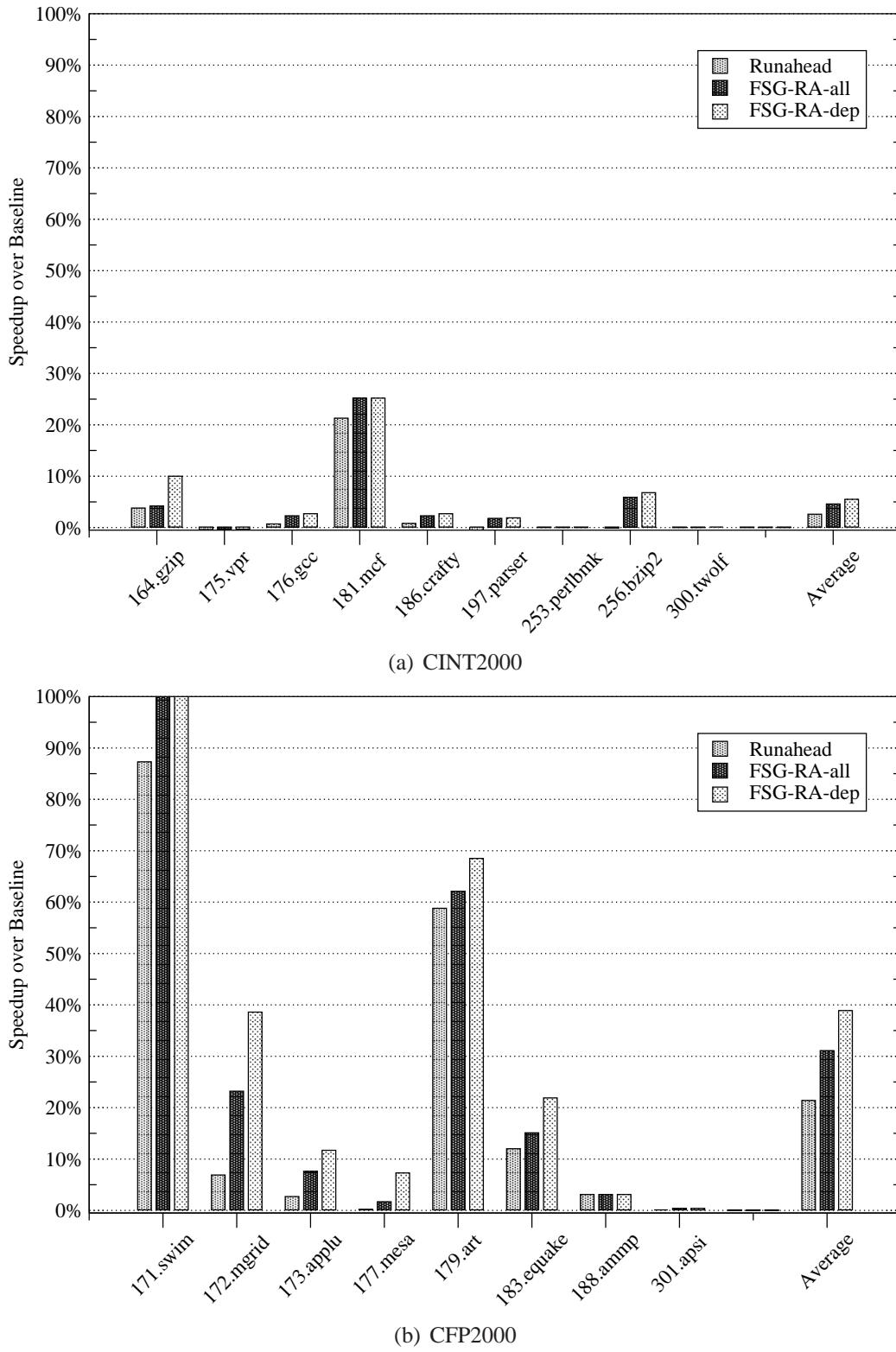

| 7.8  | Performance of 4 Models                       | 123 |

| 7.9  | $\Delta$ Performance                          | 124 |

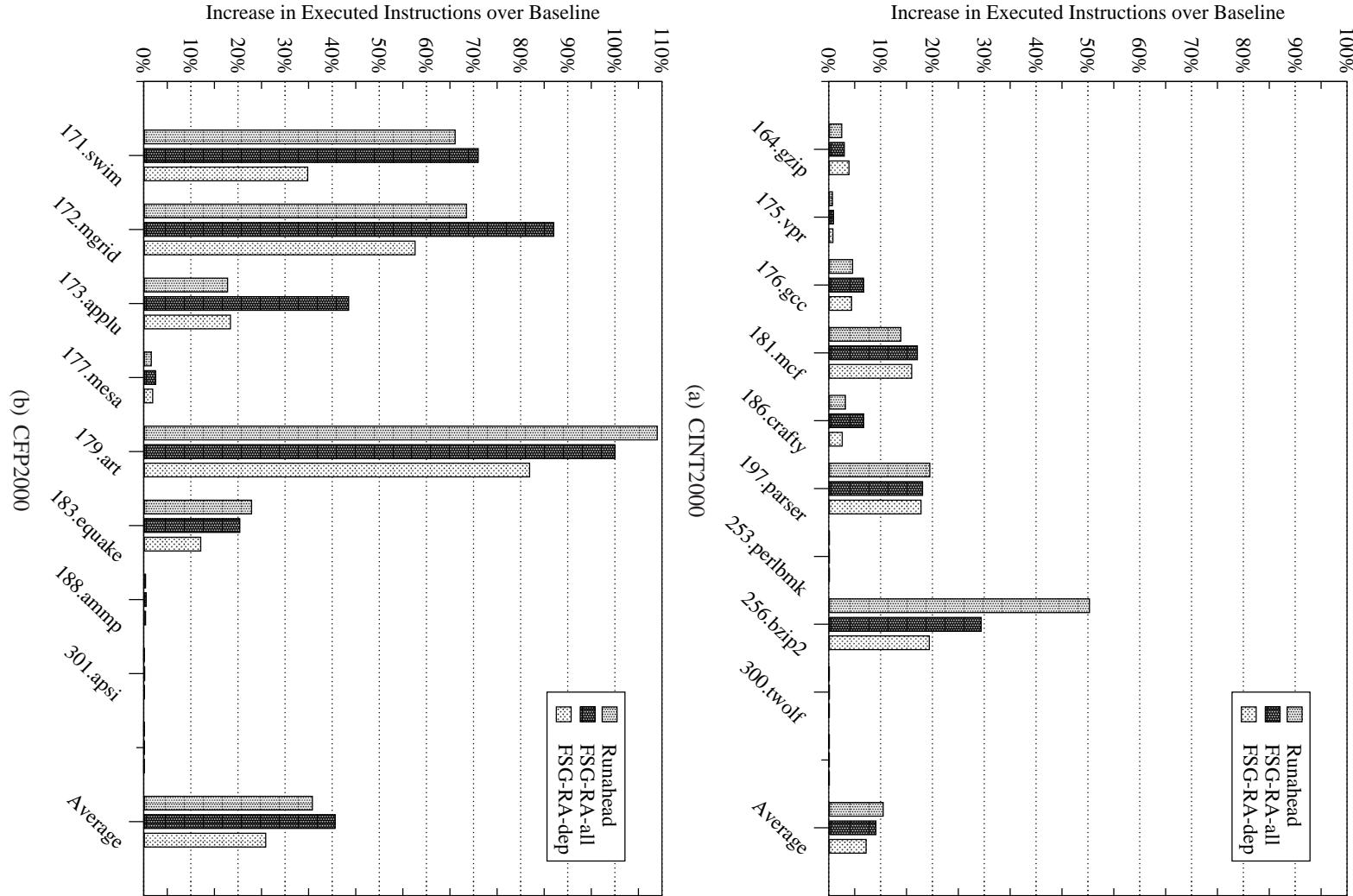

| 7.10 | $\Delta$ Number of Instructions               | 126 |

# List of Tables

|     |                                                    |     |

|-----|----------------------------------------------------|-----|

| 6.1 | Machine Configurations . . . . .                   | 87  |

| 6.2 | CINT2000 Branch Prediction Accuracies(%) . . . . . | 90  |

| 6.3 | CFP2000 Branch Prediction Accuracies(%) . . . . .  | 91  |

| 7.1 | Machine's configurations . . . . .                 | 122 |

| 7.2 | SPEC CINT2000 Efficiencies . . . . .               | 128 |

| 7.3 | SPEC CFP2000 Efficiencies . . . . .                | 128 |

| 7.4 | CFP2000 Branch statistics in FSG-RA-all . . . . .  | 129 |

| 7.5 | CINT2000 Branch statistics in FSG-RA-all . . . . . | 130 |

# Chapter 1

## Introduction

### 1.1 Motivation

Out-of-order and speculative executions have been the hallmark of high performance superscalar processors which dominated a large variety of systems from laptop computers to workstations and servers during the last decade. Processors utilizing these mechanisms need to handle processor states properly. For instance, if an exception occurs or a speculation misses, the processor state must be restored to a previous correct point to maintain the correct semantics. Proper manipulation of processor states is crucial for the successful implementation of speculation in contemporary processors [21, 47].

In this dissertation, we present a new state paradigm in which the processor is aware of the in-order, speculative and architectural states [24] on an individual data location basis, rather than with respect to a particular point in the program’s execution. We refer to the traditional processors which adopt a lump-sum approach with respect to the processor state as *Coarse-grain State Processors (CSP)*, and those which can classify individual data locations belonging to a particular state as *Fine-grain State Processors (FSP)*. We

illustrate that if appropriate mechanisms are implemented to answer queries regarding the current state of data values on an individual basis, it is possible to salvage part of the work done during speculative execution after a mis-speculation, or, even better yet, to continue execution without a roll-back and recover only the damaged part of the state *in parallel with the execution of useful instructions*.

Various micro-architecture techniques that salvage work from a failed speculation attempt [48, 10, 44, 36], as well as reducing branch mis-prediction penalty [62, 16], all implement a variation of a fine-grain state maintenance mechanism. However, to the best of our knowledge no one to date pointed out the commonality of these micro-architectural mechanisms and named it. Furthermore, very few existing techniques [62, 16, 61] harvest the performance benefits of overlapping the state recovery with useful instruction execution.

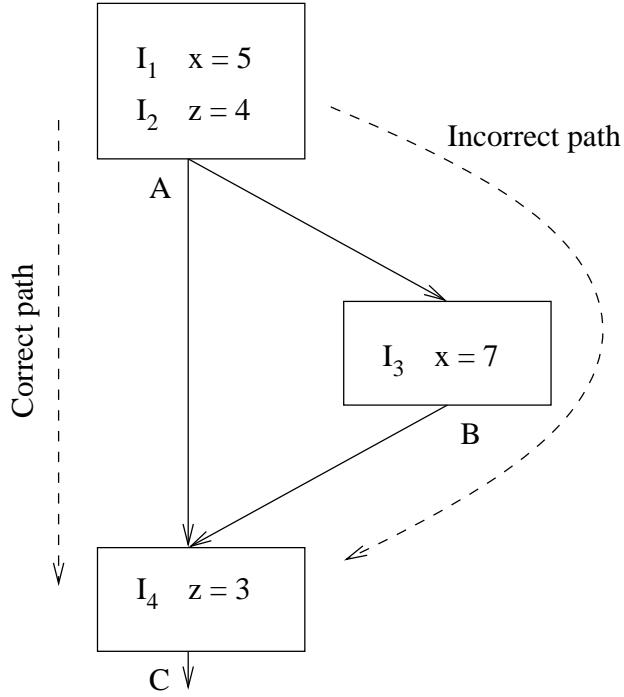

In order to better illustrate this perspective, consider a simple example shown in Figure 1.1. Assume that the processor mis-predicted the branch instruction and reached point *C*. A processor that has the concept of only a coarse grain state needs to roll back to point *A*, restore the state to the in-order state at that point, and re-execute instruction  $I_4$  to arrive at point *C* with a correct architectural state. On the other hand, if the processor knows which data values have been modified speculatively, it has two options. It can either restore the state as before by rolling back to point *A* but skip the execution of instruction  $I_4$ , i.e., salvage part of the work done during the speculative execution, or continue executing past point *C* without restoring the state, but clearly identify which values that make-up the

**Figure 1.1. Mis-speculation and its effect on state**

architectural state at point *C* have been damaged during the speculative execution (i.e.,  $x$ ) and block the references to those locations until their correct values are restored.

For most applications, rolling back and re-using salvaged results provide only limited benefits [35]. This is because the salvaged instructions may not be on the critical path of the program to shorten the execution latency when their results are reused. Furthermore, skipping over a subset of instructions is not easy and in general requires sophisticated micro-architecture techniques [8]. A majority of these techniques would pose significant design complexity in a processor implementation. Alternatively, continuing execution in parallel with the recovery of damaged values is quite feasible because all that is needed is the capability to identify the part of the state that is damaged and the means to restore these

values on an individual basis. If the recovery process can be overlapped with the useful execution, this technique can significantly reduce and in some cases completely eliminate the performance penalty of mis-speculations.

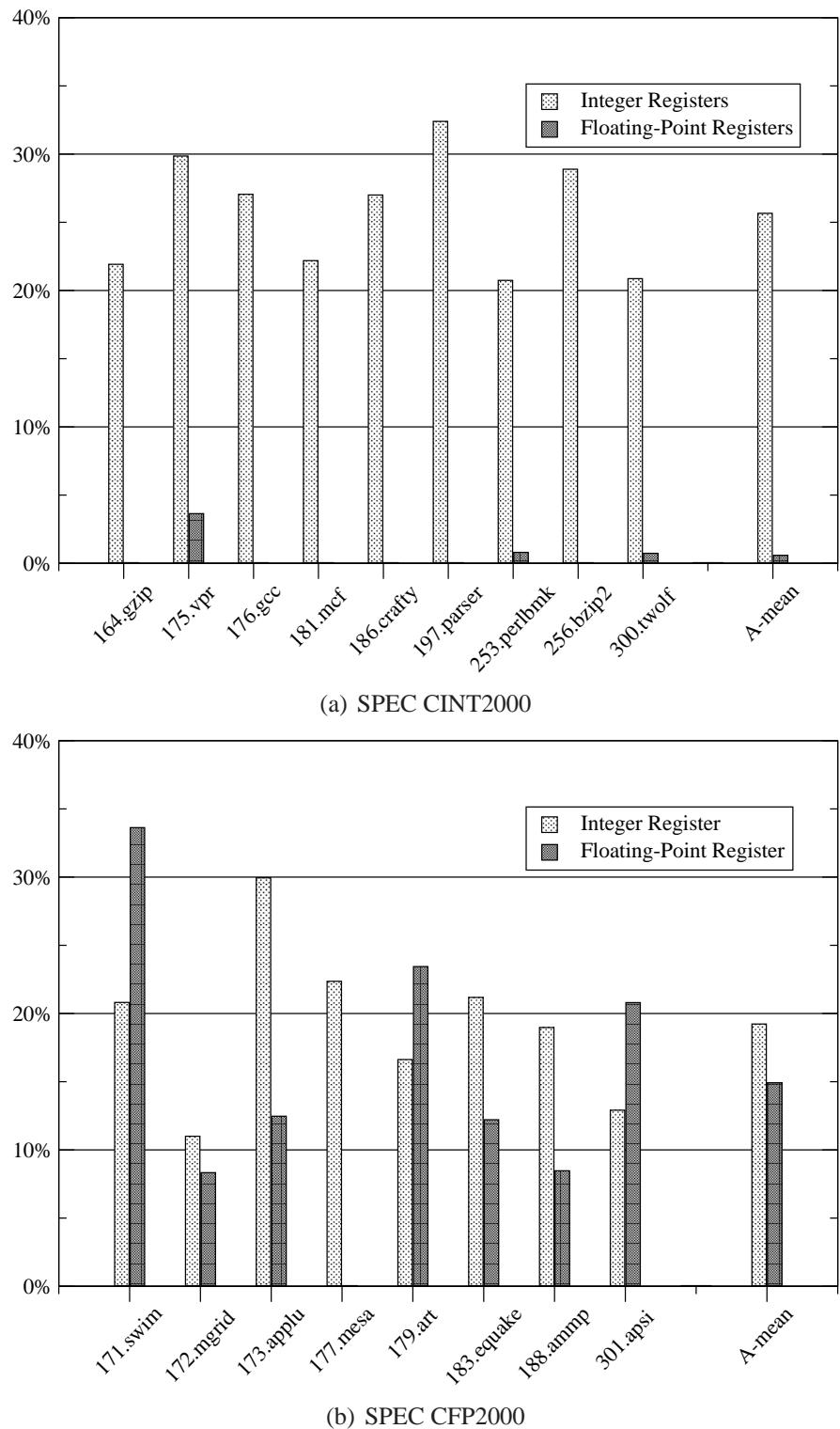

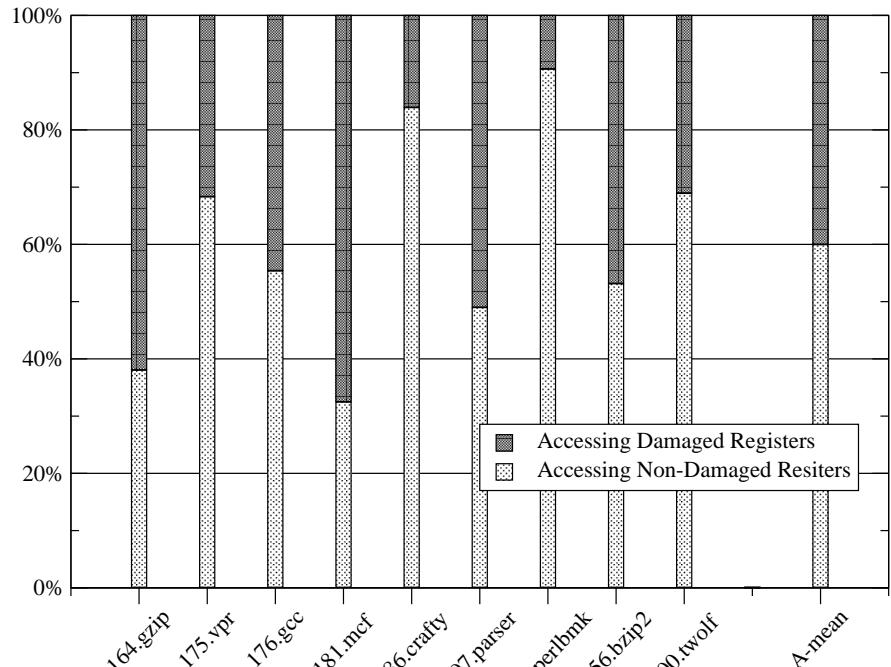

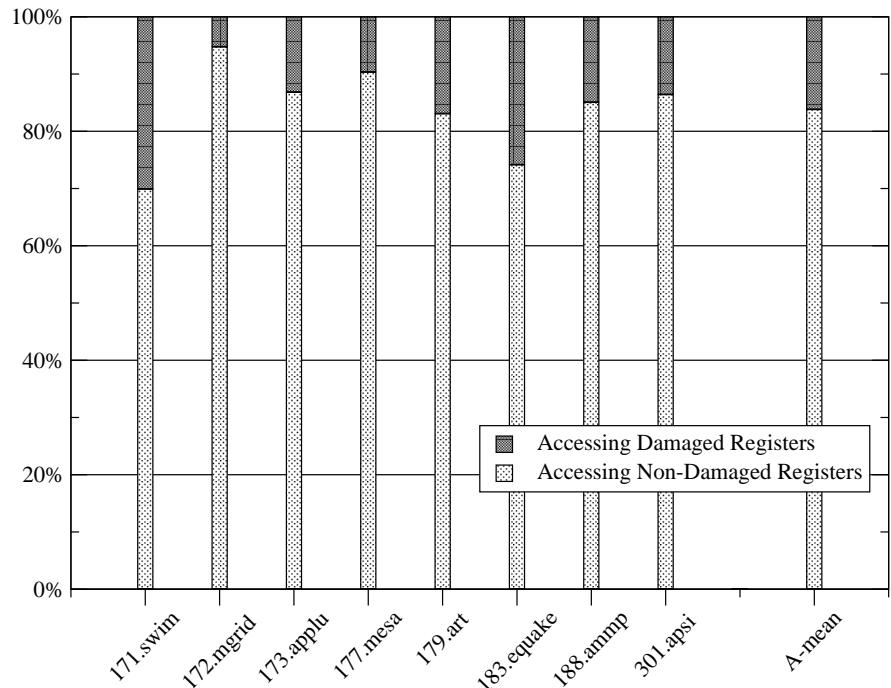

Our experimental results show that values modified speculatively along the mis-predicted branch path are only a small part of the whole architectural state. Figure 1.2 illustrates that on an average the wrong speculative state upon branch mis-predictions of 17 SPEC2000 CPU benchmarks accounts for around 20% of the whole architectural state. Moreover, our experimental results show that more than 60% of the newly fetched instructions from the correct branch path do not reference those damaged values. Illustrated in Figure 1.3, on average only 18% and 40% of instructions along the correct path of a mis-predicted branch will reference damaged register values in CFP2000 and CINT2000, respectively.

As we can see, there exists a large potential for improving the performance. Upon a mis-speculation, an FSP which is aware of the processor state on an individual basis can potentially continue processing execution before the whole process state at the mis-speculation point is restored. For this purpose, newly fetched instructions accessing incorrect speculative values need to be blocked until the correct data values are restored. On the other hand, more than 60% instructions, which access only correct values, will be able to execute while the state recovery continues. Thus, the long latency of the branch mis-prediction recovery can be overlapped with those useful instructions. *Under ideal circumstances an FSP can achieve a zero-latency recovery if there are enough independent instructions.*

Figure 1.2. Percentage of Speculative State upon Mis-predictions

(a) SPEC CINT2000

(b) SPEC CFP2000

**Figure 1.3. Distribution of References to Damaged/Non-Damaged Registers upon Mis-predictions**

## 1.2 Research Goals

FSP breaks the main limitation of the state maintenance in CSP, which cannot utilize correct values within the architectural state when an exception occurs. Although retaining the usable results has been a significant focus in a number of recent proposals [48, 44, 35], most of these proposals have provided ad-hoc solutions tailored to the specific problem at hand. The fundamental concept of fine-grain state handling provides a key insight into the design of future systems where a systematic approach can be employed to separate usable values from damaged values. Doing so can enable researchers to design processors which can aggressively pursue optimization opportunities upon an exception without waiting to restore the whole state to a known point. In this dissertation, our first research goal is to propose a general framework of fine-grain state handling. We define an FSP having the following properties:

### 1. Identification property:

The processor can identify an individual data item such as a register file entry or a memory location as belonging to the *in-order* or *speculative* state, or as a *damaged* value;

### 2. Block and shelve property:

The processor can block an instruction which references damaged values by shelving it until the damaged values are corrected;

### 3. Correction property:

The processor has the means to correct damaged locations on an individual basis after a mis-speculation;

#### 4. **Unblocking property:**

The processor can wake-up and execute shelved instructions which reference damaged values upon restoration of the damaged values in an arbitrary order;

#### 5. **Parallelism-in-recovery property:**

The processor can overlap the restoration of damaged values with the execution of instructions which do not reference damaged values. In other words, upon a mis-speculation, execution can continue with a partially correct state as the damaged values are repaired. This novel concept allows mis-speculation recovery to become free if there is independent work to do for the processor.

The design space of FSP is quite large. In principle, it can be applied in many different kinds of speculative execution environments by exploring the parallelism in mis-speculation recovery to improve performance. In this dissertation, we demonstrate that the FSP concept is applicable for both the control speculative execution and the value speculative execution. For this purpose we evaluate two FSP models: regarding control speculation the technique of Eager branch Mis-prediction Recovery, and for value speculation the technique of Fine-grain State Guided Runahead Execution.

Eager branch Mis-prediction Recovery (**EMR**) illustrates how one can apply the FSP concept for control speculation. In a nutshell, a traditional CSP either checkpoints the state

at branches for faster recovery, or sequentially re-constructs the in-order state at the mis-predicted point by waiting until the mis-predicted branch reaches the head of the reorder buffer. It cannot restart the execution from the correct path until the whole state at the mis-predicted branch is fully restored. However, the state checkpointing scheme is costly and the state re-constructing scheme is slow.

In contrast to the traditional schemes, EMR allows continuing the execution with a partially correct state, allowing branch mis-prediction recovery overlap with useful execution. The required hardware of EMR is modest. The hardware cost can be estimated roughly as the cost to save the checkpoints of the processor states. Comparing with the traditional checkpointing scheme, EMR needs to create the checkpoints only upon the mis-predicted branch instruction, instead of on every branch instruction.

Our second technique to illustrate the effectiveness of the concept of FSP investigates value speculation by using Runahead execution. Runahead execution was first proposed by Dundas and Mudge [14] for in-order processors and later applied to out-of-order processors by Mutlu *et al.* [37]. It is an effective method to tolerate rapidly growing memory latency in a superscalar processor. In this technique, When the instruction window is blocked by an L2-cache missing load instruction, the processor enters the “runahead mode” by providing a bogus value for the blocking load operation and pseudo-retiring it out of the instruction window. Under the “runahead mode”, all the instructions following the blocking load are fetched, executed, and pseudo-retired from the instruction window. Once the blocking load instruction completes, the processor rolls back to the point it entered the “runahead mode”

and returns to the “normal mode”. Though all instructions and results obtained during the “runahead mode” are discarded, the lookahead execution warms up the data cache and significantly enhances the memory level parallelism.

As it can be seen, Runahead execution behaves as a value speculation during which part of the state will become damaged. After the correct value of the blocking load instruction is fetched from the main memory, the Runahead processor, which is a CSP, has to roll back to the missing point and restart the execution with the correct processor state.

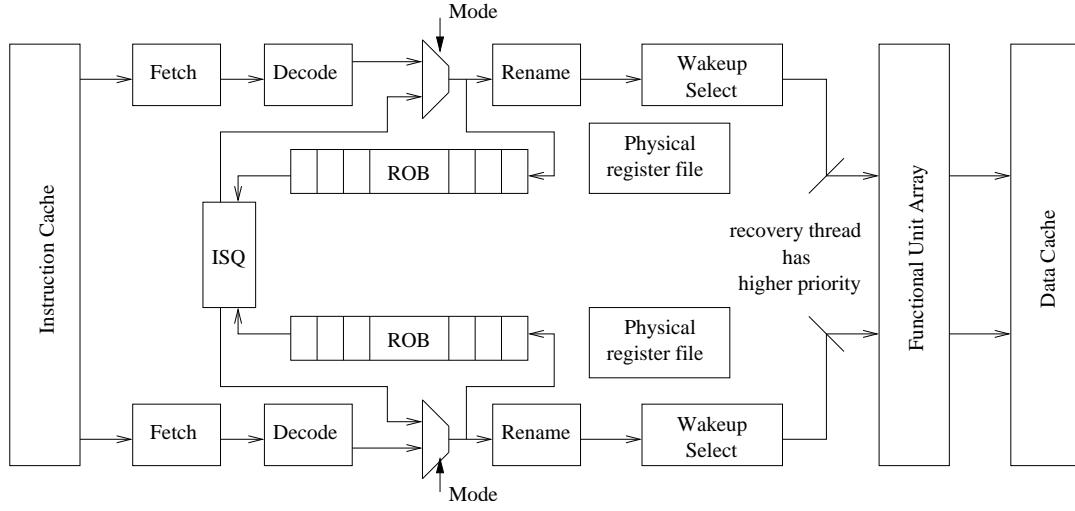

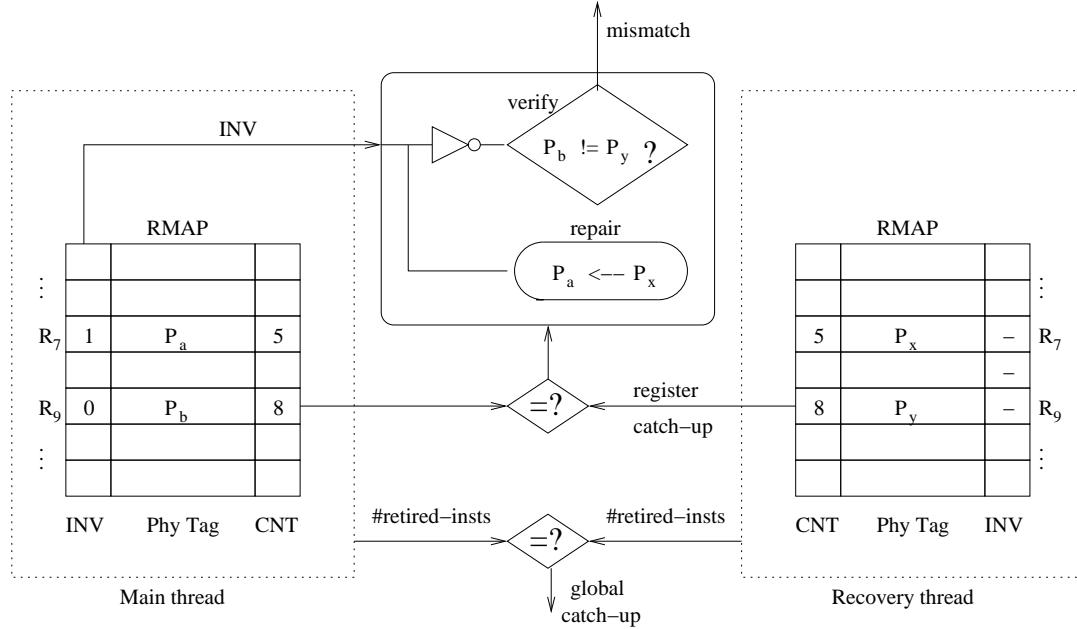

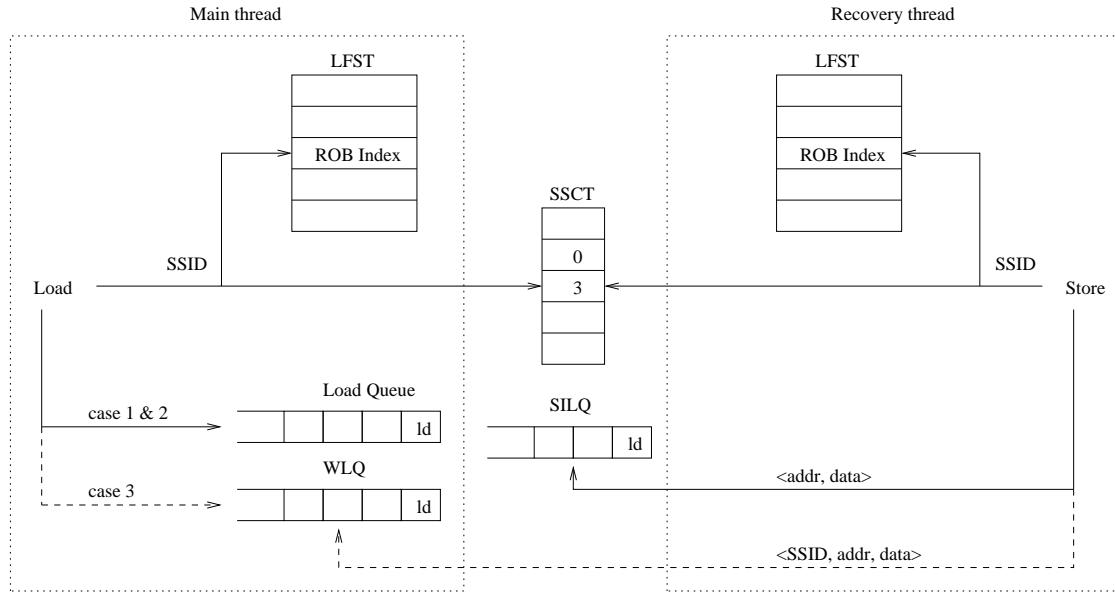

Application of FSP concepts in this realm results in a fine-grain state technique called Fine-grain State Guided Runahead execution (**FSG-RA**). FSG-RA is implemented as an SMT-like multi-threaded processor. When the missing load is resolved, FSG-RA is able to continue executing new instructions with a partially correct state, without rolling back. On the other hand, it only needs to re-execute those miss dependent instructions to repair the incorrect values updated during the “runahead mode”. Furthermore, it can execute those instructions via an idle thread, in parallel with executing the newer instructions by the original thread. Thus, FSG-RA can improve the single-thread program’s performance by exploiting the parallelism in the Runahead execution recovery in a multi-thread processor environment.

The concept of the fine-grain state is natural to reason about speculative executions and optimize speculative efforts. Comparing with the traditional CSP, our proposed FSP models, EMR and FSG-RA demonstrate that such an approach can provide impressive speed-ups without difficulties to scale processor key elements. With the fine-grain state

concept, mis-speculation recovery essentially becomes free if there is enough independent work to do for the processor. We therefore believe that the concept of FSP will open up new and exciting research opportunities in the micro-architecture community.

### 1.3 Dissertation Organization

The remainder of this dissertation is organized as follows. Chapter 2 presents the background for this dissertation. In Chapter 3, the simulation and experimental setup of this work is described. In Chapter 4, a taxonomy of FSP is introduced and related work are summarized and classified based on the taxonomy. Next, Chapter 5 introduces the design space of FSP and a general framework in which the concept can be implemented. This chapter also compares FSP and CSP regarding to the control speculation and the value speculation at a high level. Two FSP models, EMR and FSG-RA, based on the proposed general framework, are introduced in Chapter 6 and Chapter 7, respectively. Finally, a summary and the conclusion are given in Chapter 8.

# Chapter 2

## Background

This chapter is devoted to presenting a foundation for understanding this dissertation work. First, we discuss out-of-order execution and speculative execution as employed in contemporary processors. Then, the concept of processor states is illustrated. Next, we describe the traditional state maintenance and recovery mechanisms. Finally, the effect of register renaming technique on state recovery is presented.

### 2.1 Out-of-order Execution and Speculative Execution

Out-of-order execution and speculative execution are two milestones in the evolution of modern microprocessor architectures. These two techniques explore instruction level parallelism to achieve great performance.

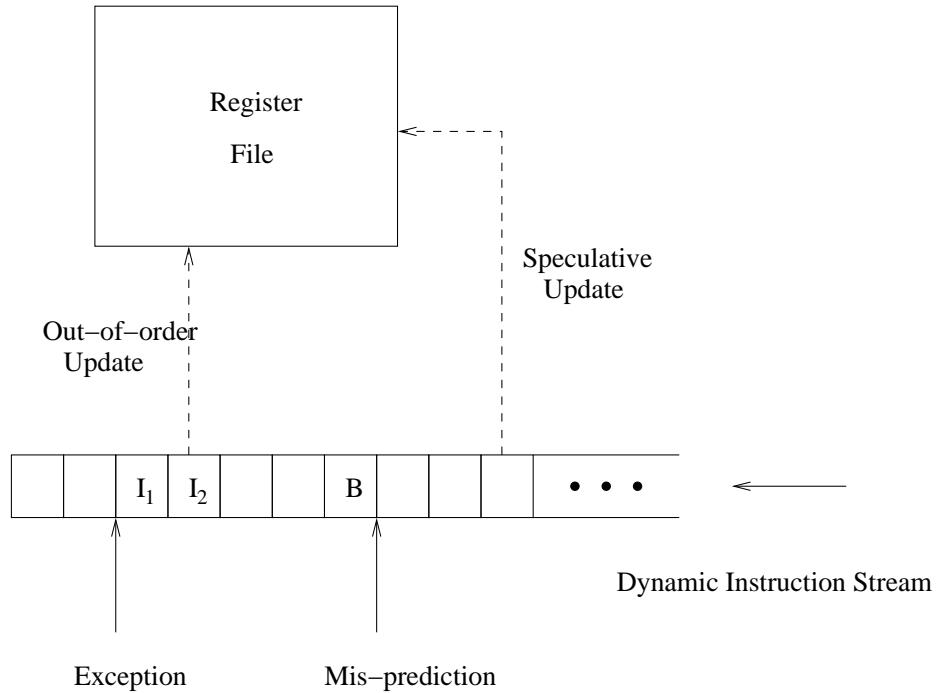

Out-of-order execution breaks the limitation of the strict sequential execution defined by the program order. Instead of waiting for previous instructions to be finished, an instruction is issued and executed once its operands are ready. Given enough computing resources, a processor can issue multiple independent instructions out of program order to exploit parallelism at the instruction level. However, an out-of-order executed instruction might

modify the processor state before it should. In such a case, the processor state will not be consistent with the sequential execution model. For example, illustrated in Figure 2.1, suppose that instruction  $I_2$  executes before  $I_1$  out of order, and writes the result to the register file before  $I_1$  executes. If later  $I_1$  raises some exception, *e.g.*, a page fault, then the modification to the state introduced by  $I_2$  needs to be reverted, before proper exception handling function is invoked.

**Figure 2.1. Exception and Mis-speculation Boundaries**

Speculative execution is another important technique for modern microprocessors. There exists several different kinds of speculation techniques, such as control speculation, value prediction, and load speculation. Let us use the control speculation as an example to illustrate the effect of speculation on the processor state.

Control speculation is a technique which is based on the prediction of the direction and

the target address of branch instructions. Without control speculation, a processor has to stall upon encountering a branch instruction until its target address and direction become known. Given that on an average there is a branch instruction in every 3~5 dynamic instructions [34], it is not acceptable to stall the instruction stream upon each branch in a modern wide-issue superscalar processor. With control speculation, the target of a branch instruction is predicted based on the history pattern of dynamic branch instructions. The dynamic instruction stream can continue along a speculative path even before that branch is executed. Though a significant body of branch prediction methods has provided us with increasingly better prediction accuracies [59, 33, 50, 9, 23], branch predictors cannot be perfect. If a prediction is wrong, all instructions along the wrong path (i.e., following the branch  $B$  in Figure 2.1) have to be flushed from the pipeline. Accordingly, modifications to the processor state introduced by those speculatively executed instructions need to be eliminated.

Once an exception or a mis-speculation occurs, the machine needs to repair its state. This process is the state recovery. The machine in Figure 2.1 needs to roll back precisely to the exception boundary before  $I_1$ , if instruction  $I_1$  brings an exception. Or, it needs to roll back to the mis-speculation boundary after  $B$  if the conditional branch  $B$  is mis-predicted (Note that the precise recovery point for  $B$  is the right boundary of the last delay slot instruction, if the delayed branch semantics is used.).

## 2.2 Processor States

In order to support out-of-order and speculative execution models and be able to recover from exceptions and mis-speculations, modern superscalar processors must be aware of different machine states, namely, in-order, speculative and architectural states [24] so that processor can always use the correct state for any externally visible changes in data locations and maintain correct program semantics.

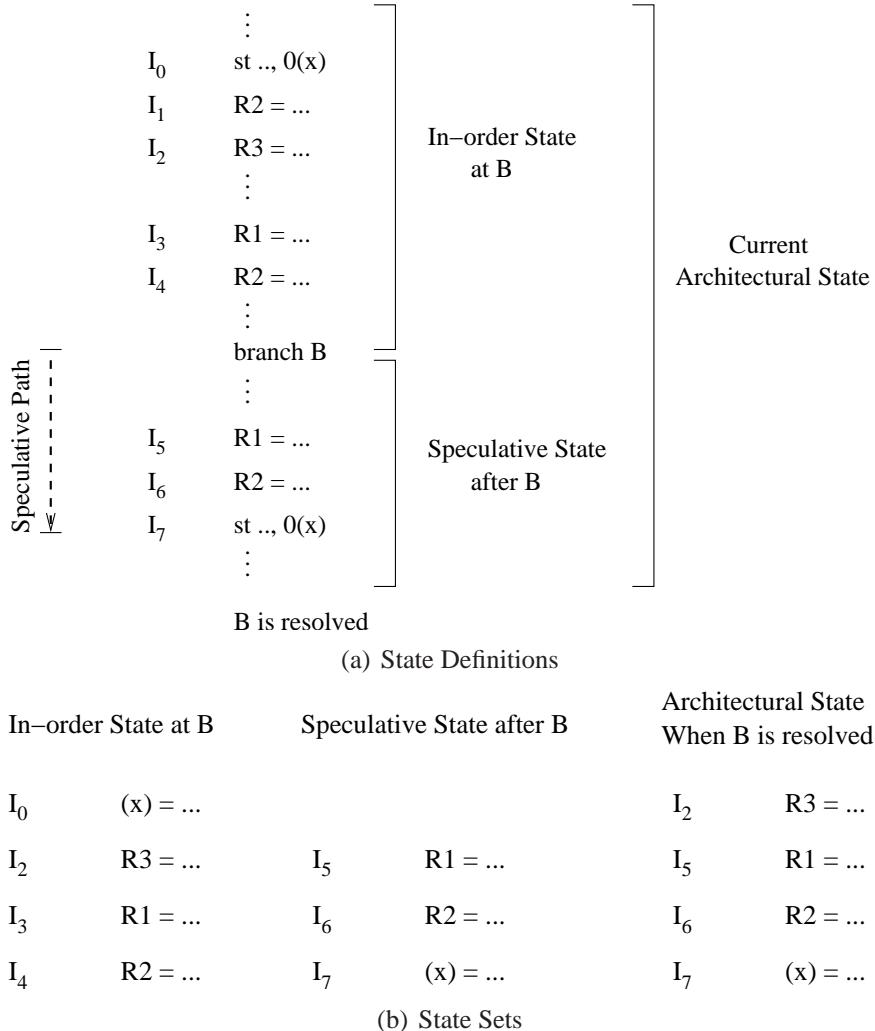

The processor state contains the full set of architectural registers or logical registers that are visible at the ISA architecture level of the processor and the memory system. Let us consider Figure 2.2 which illustrates the different states when a branch is speculatively executed. For simplicity, assume that the architectural register file has 3 registers,  $R1 \sim R3$  and the memory has only one location at address  $x$ .

We define the in-order state as the state that would have been reached if the program is executed in program order, up to the point of interest, and the speculative state as the set of values produced that have not been committed. As it should be clear, newer instructions should use the values from the in-order state if the values have not been modified (i.e., they are not part of the speculative state) and should use values from the speculative state otherwise. The architectural state is defined as the union of the in-order and speculative states, and conveniently describes the set of values which any speculatively fetched instruction should reference. For example, in Figure 2.2 the set of values produced before the branch is defined as the *in-order state at B*, the set of speculative values produced after B is defined as the *speculative state after B*, and the architectural state at the point of

branch resolution is described as the *current architectural state*. Obviously, the in-order state at B is the same state as the architectural state when the branch has been fetched.

**Figure 2.2. In-order, Speculative and Architectural States upon Speculation**

As it can be seen from the figure, the in-order state at B includes  $x$ ,  $R3$ ,  $R1$  and  $R2$  which are defined by instruction  $I_0$ ,  $I_2$ ,  $I_3$  and  $I_4$ , respectively. Let us express it as  $\{x(I_0), R3(I_2), R1(I_3), R2(I_4)\}$ . Note that the assignment to  $R2$  in  $I_1$  is superseded by the assignment to  $R2$  in  $I_4$ . Therefore, it does not belong to the in-order state at B.

Assignments to  $R1$ ,  $R2$  and  $x$  in instructions  $I_5$ ,  $I_6$  and  $I_7$  make up the speculative state after B,  $\{R1(I_5), R2(I_6), x(I_7)\}$ , because they are speculatively executed instructions and they are control depended on B. Any newer instructions after this code sequence will reference the state  $\{R3(I_2), R1(I_5), R2(I_6), x(I_7)\}$ , which is the architectural state combining the in-order state at B and the speculative state after B.

If the speculation is correct where B is resolved, all assignments along the speculative path become non-speculative. The speculative state becomes part of the in-order state, because the speculative path after B is the correct program stream. The current architectural state also becomes the in-order state at this point. In contrast, if B is mis-predicted, then the speculative execution was wrong. The processor needs to repair the incorrect architectural state back to the correct in-order state at B.

## 2.3 State Maintenance and Recovery

Traditionally, there have been two kinds of state maintenance and recovery mechanisms. One is referred to as the *State re-constructing* mechanism proposed by Smith and Pleszkun [47]. The other is referred to as the *Checkpointing* mechanism proposed by Hwu and Patt [21].

### 2.3.1 State re-constructing

To address the problems of out-of-order execution and precise interrupts in pipelined processors, Smith and Pleszkun proposed the reorder buffer (ROB), the history buffer and the future file designs to support the state recovery and maintenance. We refer to them all

as the *State re-constructing* mechanisms.

### Reorder Buffer

The reorder buffer (ROB) is implemented as a circular buffer with a head pointer and a tail pointer. Shown in Figure 2.3, once an instruction is fetched and decoded, it is inserted into the tail of the ROB. After it is executed, its result and the exception flag are stored in the corresponding entry in the ROB. When this instruction reaches the head of the ROB, it will write its result to the logical register file and release the entry, if it is exception-free; Otherwise, the processor needs to flush the pipeline and restart the execution.

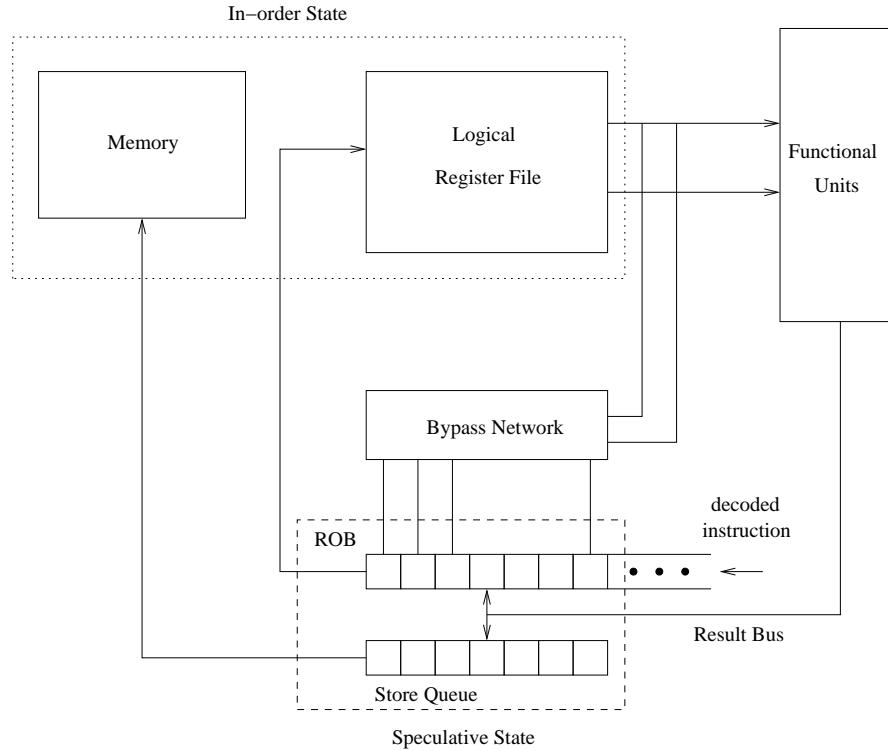

Similar to other producer instructions, a store instruction is only allowed to commit its result to the memory hierarchy, including the cache and the main memory, when it reaches the head of the ROB. This is, at this point, all previous instructions, including all memory operations, are already committed and known to be exception-free. Before it is committed to the memory, a store instruction can keep the value to be written to the memory in its allocated ROB entry, or, generally, in some associated buffer, *e.g.*, the store queue.

From the point of view of states, one can vision that the logical register file always has the in-order register state, and the memory system always has the in-order memory state. On the other hand, the ROB entries store the speculative state of registers, and the store queue entries store the speculative memory state. The union of the in-order state and the speculative state is the processor's architectural state.

Any newly fetched instruction will reference the architectural state of registers by accessing the logical register file and the ROB entries simultaneously. In order to do that,

**Figure 2.3. Reorder Buffer**

processor implements the bypass paths from the ROB entries to the register file. In order to reference the architectural memory state, load instructions need to access the memory system and the store queue simultaneously.

In a speculative processor with a ROB, once an exception occurs, the exception is not handled until the instruction triggering the exception reaches the head of the ROB. At this point, it is easy for the processor to roll back the damaged architectural state into the correct in-order state, because the desired state is already stored in the register file and the memory. The processor simply discards the wrong speculative state stored in the ROB and the store queue, and then restarts from the exception point with the correct in-order state.

In another words, the in-order state at the exception point is constructed by waiting for

the instruction rising the exception to reach the head of the ROB, and retiring previous instructions one by one in the program order. This is the reason why the technique is referred to as the *State re-constructing* mechanism.

### History Buffer

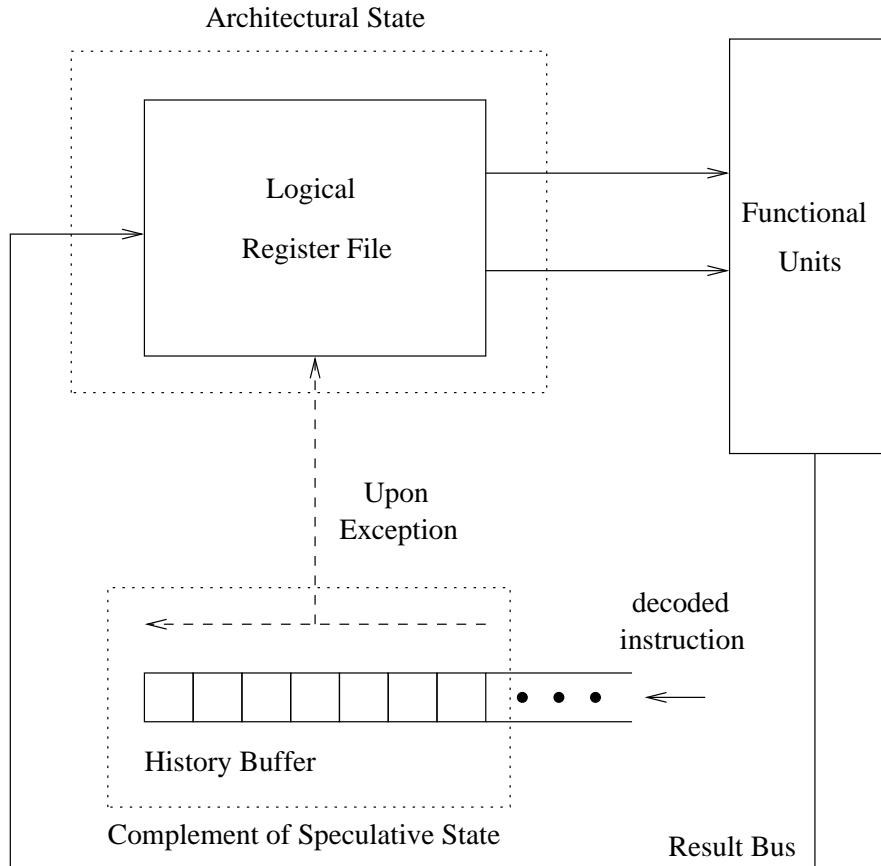

In the above reorder buffer mechanism, the speculative register state is stored in the ROB entries, and the in-order register state is always present in the logical register file. Alternatively, the register file can be used to store the architectural register state and the history information of the in-order register state can be buffered to support the state recovery if an exception occurs. This method is called the history buffer technique.

The history buffer is implemented in a similar way to the reorder buffer, illustrated in Figure 2.4. The history buffer is a circular buffer which has a head pointer and a tail pointer. Once an instruction is fetched and decoded, it is assigned an empty entry and inserted into the tail of the history buffer. Meanwhile, if it is a register producer instruction, the current value of its destination register is read from the register file and stored into the allocated entry. After the instruction is executed, the execution result is written into the register file immediately, and the exception flag is recorded in the history buffer entry.

From the point of view of states, the logical register file in the History Buffer mechanism always represents the latest architectural state of registers. The previous in-order values of all speculatively executed instructions' destinations are stored in the history buffer entries, in program order. In other words, the history buffer represents the *complement* set of the speculative register state.

**Figure 2.4. History Buffer**

When an instruction reaches the head of the history buffer, its history buffer entry can be safely released if there are no associated exceptions. If this instruction's exception flag is set, the pipeline of the processor is stalled, and the state recovery process is invoked. In order to restore the correct state, the processor empties the history buffer entries one by one from the tail towards the head, and restores each saved history value back into the register file.

After all saved previous in-order values are written back into the register file in reverse program order, the wrong speculative state in the architectural state is totally eliminated,

and the correct in-order state at the exception point is restored. Once the head entry allocated for the exception instruction is scanned and processed, the processor is able to restart from the exception point with a correct in-order state.

The history buffer scheme is different from the reorder buffer scheme only with how to handle the register state. To handle the memory state, the history buffer scheme utilizes the same method as the reorder buffer scheme. That is, a store instruction only commits to the memory when all preceding instructions are committed without any exception. Before the retirement, a store instruction keeps the values to be written in the store queue. Like in the reorder buffer scheme, the memory hierarchy always represents the in-order memory state and the store queue holds the speculative memory state.

### **Future File**

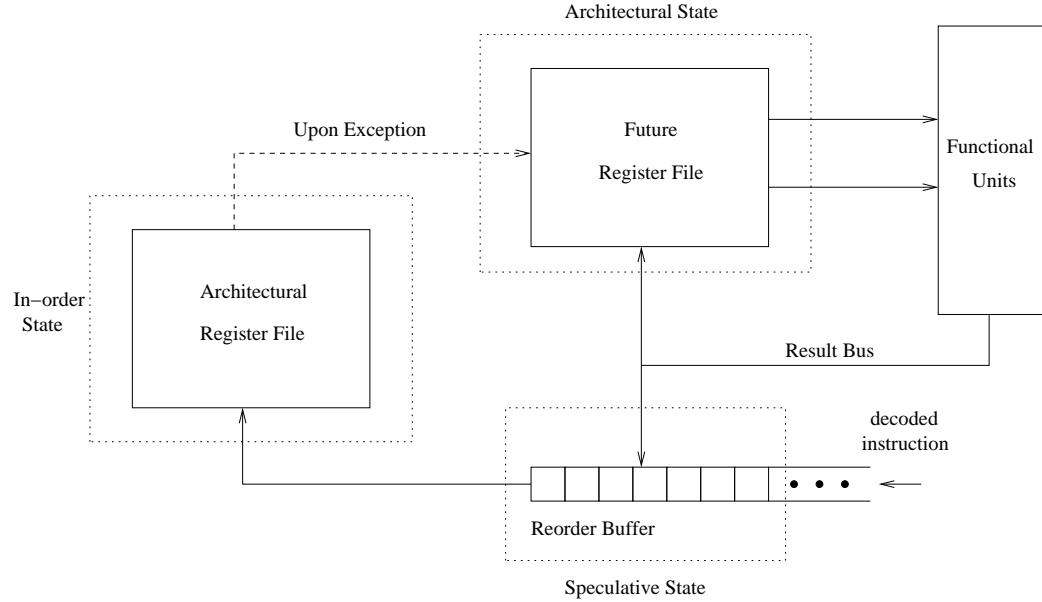

The third variant of the *State re-constructing* mechanism is the future file, an optimization of the reorder buffer implementation. The idea of the future file is to maintain two separate register files, the future file and the architectural file, illustrated in Figure 2.5. When an instruction is executed and finished, its result is written into the future file. When an instruction retires from the head of the ROB, it will update its result into the architectural file.

From the point of view of states, the future file maintains the architectural state of registers. It consists the in-order values and the speculative (future) values, so it is called the future file. The architectural file always reflects the in-order state of machine's architectural registers. If an instruction reaches the head of the ROB with an error, the architectural file

**Figure 2.5. Future File**

is then used to restore the future file. Either the whole register file is copied as a set, or only speculatively modified registers are restored. To implement the latter, those register designators associated with ROB entries are copied from the ROB's head to the ROB's tail.

As it can be seen from the figure, the future file in fact implements the functionality of the physical register file with respect to the register renaming, though Smith and Pleszkun did not use the term of the register renaming in [47]. The future file can be considered as a physical renaming register file which has the same size as the architectural logical register file. Therefore, the register renaming map table can be omitted.

In the future file scheme, the memory state is also handled in the same way as in the reorder buffer and the history buffer. The memory is always an in-order state memory, and the speculative memory state is buffered in the store queue.

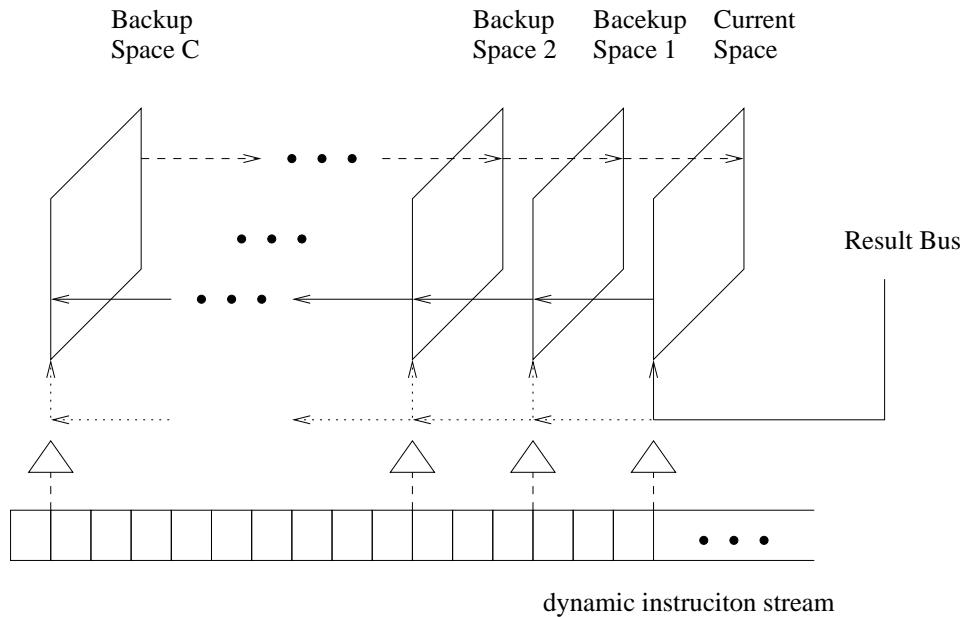

### 2.3.2 Checkpointing

An alternative to sequential re-construction of processor states is to save a snapshot of machine state at appropriate points of the execution. This approach is referred to as the *Checkpointing* mechanism, which was first introduced by Hwu and Patt [21].

With checkpointing, the processor maintains a collection of *logical spaces*, where each logical space is a full set of architectural registers and memory locations visible at the ISA level of the machine. There is only one logical space used as the *current* space for the current execution which represents the architectural state. Other backup logical spaces contain the copies of the in-order state that correspond to previous points in the execution.

**Figure 2.6. Checkpointing Maintenance and Recovery Scheme**

During the execution, the processor creates a checkpoint of the state by copying the current logical space into a backup space, as shown in Figure 2.6. Upon each checkpoint,

the effect to the current architectural state introduced by all instructions to the left of that checkpoint are allowed, and the effect introduced by all instructions to the right of the checkpoint are excluded. Therefore, each logical space represents the in-order state at the creating point. The logical spaces are maintained as a stack. If the stack is full, making a checkpoint has to wait until the oldest one is safely released. When a fault exception or a branch mis-prediction occurs, the architectural state can be restored to the in-order state at the exception point by recovering the current space back to the corresponding logical space.

Ideally, a checkpoint should be created at each instruction boundary so that a processor is able to restore the correct state if any instruction meets an exception. Otherwise, if there is no backup state available at the exception point, the processor has to roll back to the nearest checkpoint and discard some useful work. However, the cost and overhead of creating a checkpoint at each dynamic instruction boundary is too high. This is the fundamental dilemma of the checkpointing recovery mechanism.

On one hand, we need to create as many checkpoints as possible to make the exception recovery fast. On the other hand, we need to keep the cost of checkpoints as low as possible. To address this issue to some degree, Hwu and Patt distinguished fault exceptions and branch mis-predictions with respect to the state recovery, because fault exceptions actually happen much less frequently than branch mis-predictions. Accordingly, they proposed to create a checkpoint at each branch instruction for the mis-prediction recovery, and to create checkpoints at widely separated points in the instruction sequence for the fault exception

recovery.

Another issue of the checkpointing scheme is how to implement the backup spaces of the state. Generally, there are two types of techniques for implementing multiple logical spaces: *copying* and *difference* techniques.

The copying technique is normally used to create the logical space of the register state. When a checkpoint is created, the architectural register state in the current space is copied into the logical space. Since some instructions to the left of the checkpoint might have not been issued yet, the copied state is not the in-order state at that time. Therefore, the copied state needs to be updated as instructions to the left of the checkpoint complete. To avoid extra increase of the access bandwidth of the register file, each bit of the registers is implemented by  $C + 1$  physical cells, one cell for the current space and  $C$  cells for  $C$  backup logical spaces.

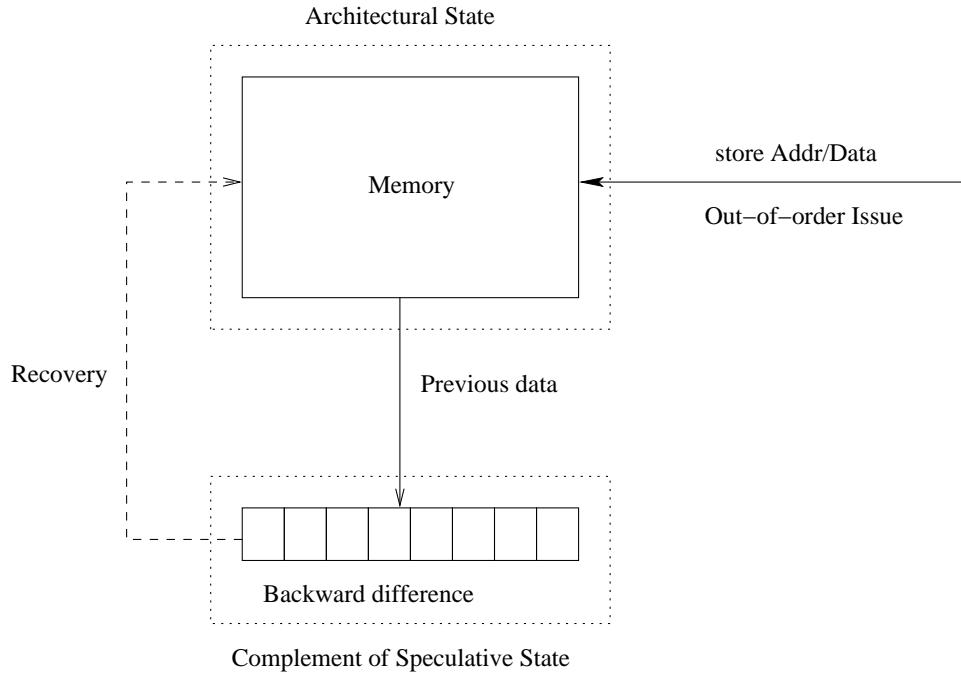

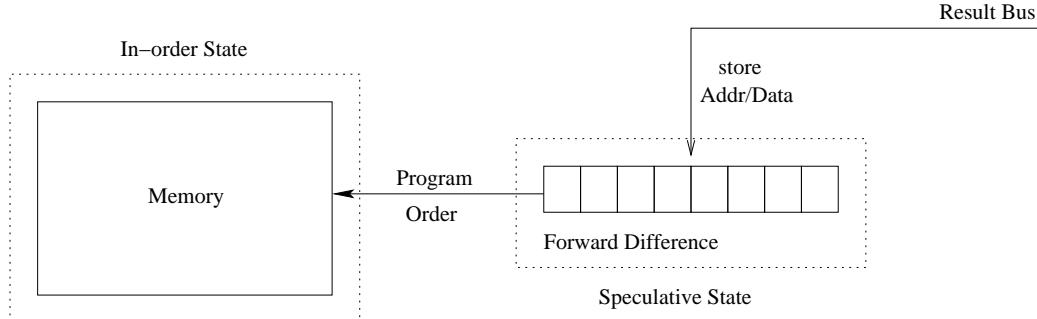

The difference technique maintains a list which records the difference of the execution state from one instruction boundary to another. Normally, the checkpoint of the main memory state is implemented via the difference technique. There are two directions a state difference can be recorded, backward and forward. Each logical space implements either the backward difference or the forward difference to manipulate the memory state.

The backward difference maintains a history value list in which each entry keeps the history value prior to the modification to the state. Figure 2.7 illustrates the memory design when a backward difference is employed. When a store instruction commits its value to the memory, the address and the previous value at this location in the memory

**Figure 2.7. Logical Space of Memory by Backward Difference**

are saved in the backward difference list. The backward difference list preserves the store instruction's committing order to the memory, not the program order they appear in the dynamic instruction sequence. As it can be seen from the figure, the main memory represents the architectural state, including the in-order state and the speculative state. The backward difference holds the complement of the speculative state. During the state recovery, the history data saved in the list are stored back to undo all modifications to the memory introduced by the wrong speculative state. Thereby the in-order state of the memory at the checkpoint can be repaired.

In contrast to the backward difference, the forward difference keeps all speculative values within a logical space, and preserves the program order of stores. Shown in Figure 2.8, when a checkpoint is created, the memory holds the in-order state at this point,

**Figure 2.8. Logical Space of Memory by Forward Difference**

and the forward difference will keep the speculative state of this logical space, until the next checkpoint is created. From this point of view, the memory manipulation scheme introduced in the previous state re-constructing mechanism is a special case of the forward difference technique on which the memory system always represents the machine's in-order memory state and the store queue keeps the speculative memory state introduced by all in-flight instructions.

## 2.4 Register Renaming and State Maintenance and Recovery

In order to eliminate WAR (write after read) and WAW (write after write) data hazards, modern superscalar processors normally utilize the register renaming technique. The design space of register renaming is large and it is beyond the scope of this work. In this work, we only consider the effect of register renaming on the state maintenance and recovery.

The reorder buffer scheme, described in Section 2.3.1, provides a straightforward implementation of register renaming. In ROB, an architectural logical register can have multiple definitions in-flight, which are kept in different ROB entries in program order. In

order to read the correct value of an operand, an instruction can associatively search the ROB and access the entry for the most recent definition of its source operand when it is issued. The ROB entries implement the renaming functionality.

Generally, processors utilize a physical register file to implement register renaming. The physical register file can be separated from the logical register file, or they can be combined together as a unified register file. In order to eliminate the false data dependences and exploit deep speculation, physical register file size will be larger than the size of the logical register file visible at the ISA level. Once a producer instruction is decoded, it is allocated a free physical register as the renaming location for its destination. This mapping of information between the logical register designator and the physical register designator is then recorded so that subsequent instructions can reference the latest value from the renaming physical register.

The mapping information is normally stored in the register map table (MAP), which is also referred to as the register alias table (RAT) [58, 20]. In a superscalar processor, if multiple instructions need to be decoded and renamed simultaneously in every cycle, then the map table, or the alias table, has to be multi-ported. For instance, if it is a 4-issue superscalar processor, then the map table needs 8 read ports and 4 write ports, assuming each instruction has two source operands and one destination.

The map table structure can be implemented in at least two ways: the RAM structure and the CAM structure [40]. The different structures have the different implications for the state maintenance and recovery.

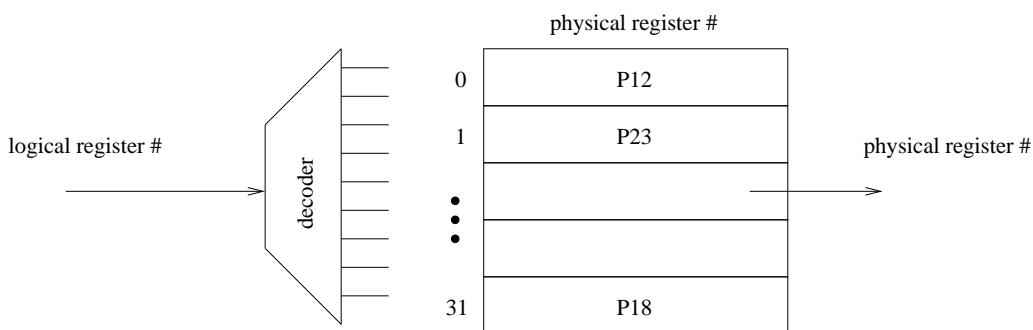

### 2.4.1 RAM-structured MAP

The RAM-structured map table is illustrated in Figure 2.9. In this structure, the total number of the map table entries is equal to the total number of the architectural logical registers. Each logical register has a corresponding entry in the map table, and the logical register's designator can be used as the index to access the table. Each entry contains a physical register designator which is allocated and associated with this logical register. The RAM-structured map table itself is implemented as a register file in which each cell holds just enough bits to specify a physical register's designator, instead of a 32- or 64-bit value.

As it can be seen, the map table represents the register state. Register values stored in the physical register file can be referenced through indices in the map table. Normally, processor employs a front-end map table as the working map table, corresponding to the current architectural state. If an exception occurs, processor needs to repair the front-end map table to restore the correct register state. The restoration process can be done via either the checkpointing method or the state re-constructing method.

Figure 2.9. RAM-structured Map Table

Examples of processors which employ a RAM-structured map table are the MIPS R10000 processor and the Intel Pentium IV processor. Regarding to the branch mis-speculation recovery, the MIPS R10000 processor utilizes the checkpointing method to manipulate the state, and the Pentium IV processor utilizes the state re-constructing method.

### MIPS R10000

The MIPS R10000 maintains a branch stack where each entry contains a complete copy of the integer and floating-point register map tables [58]. At the point of recognizing a mis-prediction, the processor restores the front-end map table from the corresponding checkpoint. While the checkpoint scheme yields fast recovery, its hardware cost can be prohibitive. Suppose there are  $N$  physical registers, and the instruction set contains 32 integer and 32 floating-point logical registers, then the size (bits) of each checkpoint is:

$$\text{Checkpoint Size} = 32 \times \log_2 N + 32 \times \log_2 N = 64 \times \log_2 N \quad (2.1)$$

If  $C$  checkpoints are implemented, then the total size of the checkpoint stack is:

$$\text{Total Checkpoint Size} = C \times 64 \times \log_2 N \quad (2.2)$$

As we can see, checkpointing the map table at each outstanding branch instruction is costly. The available space for storing the checkpoints, on the other hand limits the number of pending branches that can be in-flight. In the MIPS R10000, only 4 pending branches

are allowed to be in-flight because its branch stack has only 4 entries as shown in Figure 2.10.

**Figure 2.10. Checkpoint Stack in MIPS R10000**

To some degree, the register renaming technique makes creating checkpoints easier. Consider the original checkpoint scheme described in Section 2.3.2. When a checkpoint is created, some instructions left to this point may have not been finished yet. In order to bring this checkpoint into the desired in-order state later, the results of these instructions have to be written into the corresponding backup space when they are ready.

Using the register renaming technique, processor allocates a free physical register for each instruction with a register destination during decoding. Therefore, in-order state at a particular point can be represented as the format of the physical register designators stored in the map table at that point. The in-order values can be referenced by means of the physical register designators. Thus, updating values into the backup space can be omitted.

### Intel Pentium IV

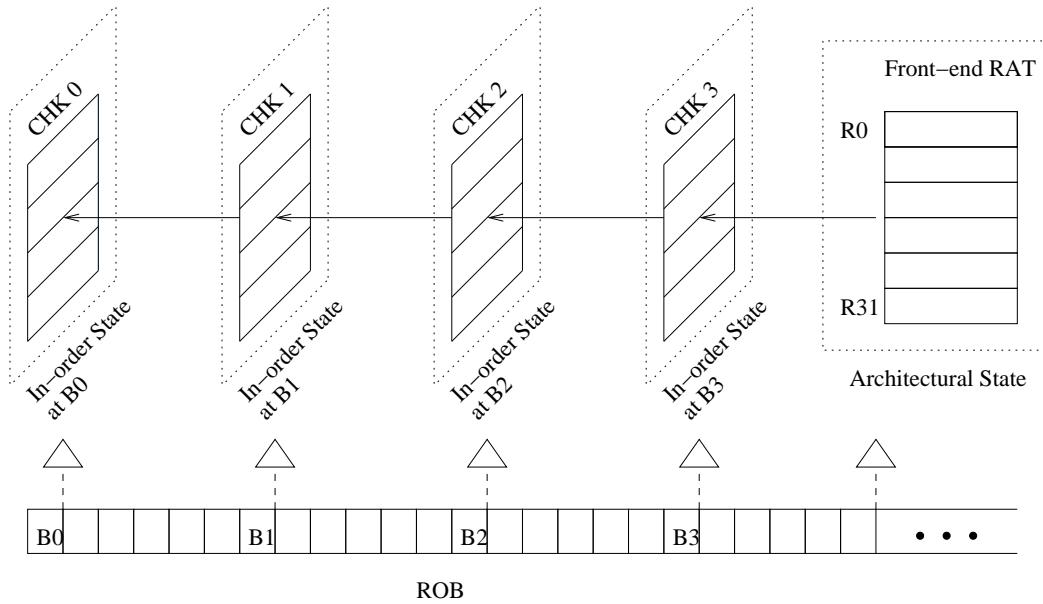

The NetBurst micro-architecture of the Pentium IV also utilizes the RAM-structure. Unlike the MIPS R10000 processor which uses a checkpointing recovery mechanism, it utilizes a state re-constructing recovery scheme. Two map tables named the front-end RAT and the retirement RAT [20] are maintained. The front-end RAT stores the architectural state and the retirement RAT stores the machine's in-order state, shown in Figure 2.11.

**Figure 2.11. State Re-constructing in Pentium IV**

Any newly fetched and decoded instruction will access and modify the front-end RAT, thus, it always contains the latest architectural state. When an instruction retires, it updates the retirement RAT to indicate that its result register is in the in-order state. The retirement logic ensures that an exception occurs only if the operation causing the exception is the oldest, non-retired operation in the machine. That is, an instruction can rise an exception

only when it reaches the head of the ROB. At this point, the machine's in-order state is also the in-order state at the exception point. Therefore, processor can restore the architectural state, or the front-end RAT, from the retirement RAT.

Although Pentium IV requires only two RAM-structured RATs, the recovery process may take a long time as renaming cannot start until all instructions prior to the mispredicted branch retire. If a long latency operation prior to the branch exists, *e.g.*, a cache miss, the mis-prediction penalty increases significantly.

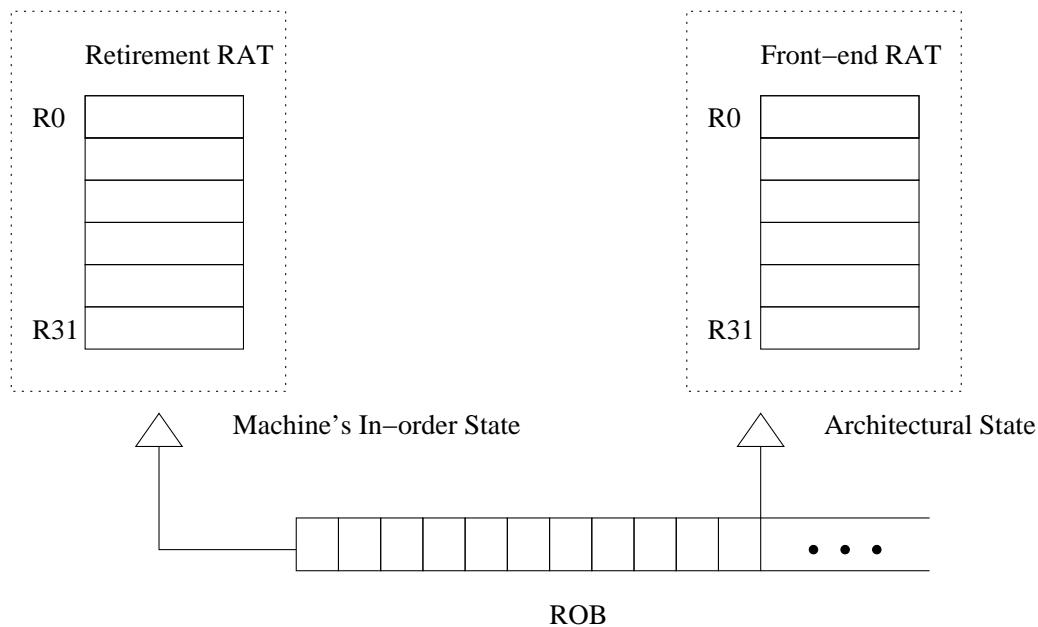

#### 2.4.2 CAM-structured MAP

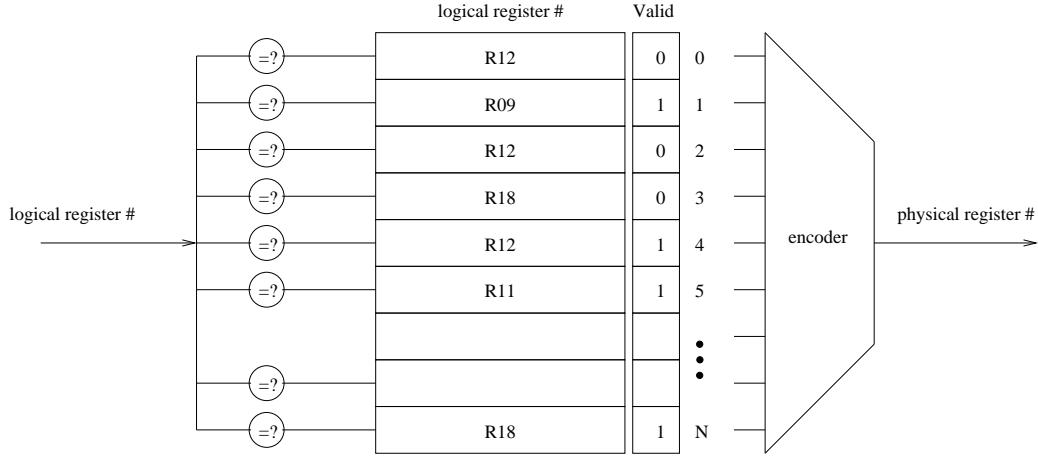

Alternative to the RAM-structured scheme, the other way to implement the map table is to use a content-addressable memory (CAM). Illustrated in Figure 2.12, in a CAM-structured map table, the total number of table entries is equal to the total number of physical registers. Each entry has two fields, the logical register designator field and the valid bit field. Since a logical register might have multiple definitions in-flight, the valid bit is always set by the latest definition. Once a logical destination register is mapped into a free physical register, this logical register number is written into the corresponding entry in the table. Also, its valid bit is set and the previous valid bit of the same logical register is located through an associative search and cleared.

When an instruction accesses the table to read its operand's renaming physical register designator, the operand's logical register number is used to search the table's logical register designator field associatively. If there is a match and the corresponding valid bit is set, then this entry's index is generated through an encoder as the renaming physical register number.

Figure 2.12. CAM-structured Map Table

The valid bit indicates the latest renaming physical register of each logical register. From this perspective, the valid bit vector presents the current architectural register state. To create a checkpoint of the register state, processor needs only to make a shadow copy of the valid bit vector. Suppose there are  $N$  physical registers, the size (bits) of each checkpoint is:

$$\text{Checkpoint Size} = N \quad (2.3)$$

If  $C$  checkpoints are implemented, then the total size of  $C$  checkpoints is:

$$\text{Total Checkpoint Size} = C \times N \quad (2.4)$$

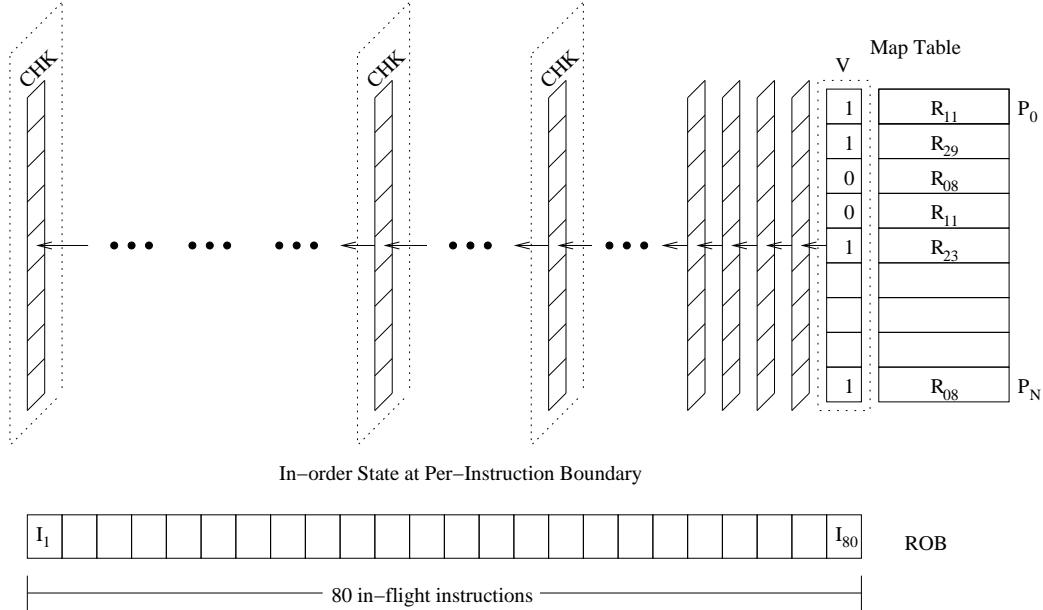

In the CAM-structure implementation, creating checkpoints is not expensive. Only valid bits, not the whole map table, need to be copied. The CAM-structure map table is utilized in the DEC Alpha 21264 [13, 26]. The Alpha 21264 supports up to 80 instructions in-

flight, and a checkpoint is created at every instruction boundary. Illustrated in Figure 2.13, it provides the capability of precise state recovery at any of the 80 in-flight instructions.

**Figure 2.13. Per-Instruction Boundary State Recovery in Alpha 21264**

Though the hardware cost of creating checkpoints with the CAM-structure map table is not too expensive, the CAM-structure itself may become a bottleneck. With the CAM-structure, the total number of entries in the map table is equal to the total number of physical registers. Moreover, processor needs to perform an associative search to access it. On the other hand, with the RAM-structure, the number of entries in the map table is equal to the number of ISA logical registers, independent of the number of physical registers, and the table access is fast. That makes the CAM-structure less scalable than the RAM-structure.

Given these observations, the CAM-structure may not scale well with future wide-issue high performance microprocessors. In this work, we mainly focus on the RAM-structure

designs with respect to the state maintenance and recovery.

## 2.5 Summary of Background

In this chapter, the basic concept of process states is described. In order to support out-of-order and speculative executions, processor needs to be aware of the in-order state, the speculative state, and the architectural state at different interest points. To recover from an exception or a mis-speculation, processor needs to eliminate the wrong speculative state, introduced within the speculative execution, from the architectural state and restore it back to the in-order state at the exception point.

Traditionally, there have been two main mechanisms to manipulate states, state reconstructing and checkpointing. Despite the fact that they appear to be drastically different, they share a common property. Both are based on the coarse-grain state concept. As we can see, any processor utilizing these mechanisms can be classified as a CFP. Upon an exception, neither of these mechanisms allows the resumption of fetching and renaming of new instructions from the correct path until the whole set of processor state is restored.

# Chapter 3

## Simulation and Experimental Setup

In this chapter the simulation tool and the experimental setup used for this dissertation are introduced and presented.

### 3.1 Simulation Tools

For processor architecture researchers, realizing novel micro-architecture designs in hardware is too expensive and time-consuming, especially at the prototype stage of development. Thus most research relies on simulation tools that can estimate the performance of the micro-architecture by simulating a variety of benchmark programs. A commonly used approach for developing micro-architecture simulators is hand coding them in a general purpose programming language. For instance, widely used in the computer architecture research community, the SimpleScalar simulator [7] is written in C and the M5 simulator [6] is written in C++.

Although writing simulators in the general purpose languages is a straightforward process, it is difficult to retarget such simulators to a modified micro-architecture or an instruction set architecture once they are built. In this work, instead of hand coding

simulators, we use the *Flexible Architecture Simulation Tool* (FAST) [38] to generate simulators automatically, in which processor specifications are written in a domain specific language called *Architectural Description Language* (ADL). FAST currently supports the MIPS ISA [41] which is also implemented in ADL.

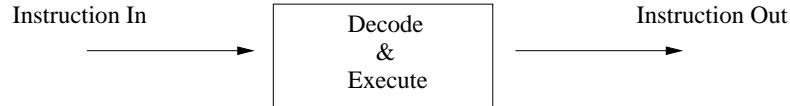

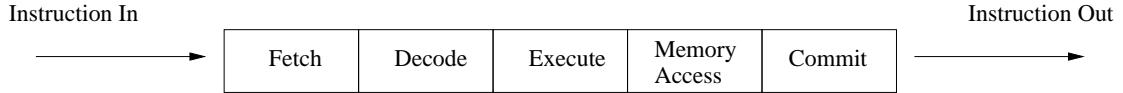

**Figure 3.1. Fast Functional Simulator**

**Figure 3.2. 5-Stage Pipeline Simulator**

Shown in Figure 3.1, Figure 3.2 and Figure 3.3, FAST is comprised of a variety of different cycle-accurate processor simulators that are from a fast functional simulator which executes instructions one by one through a simple one stage pipeline, and a 5-stage in-order pipeline processor simulator, to a complex out-of-order superscalar simulator [38]. In this work, the out-of-order superscalar simulator is mainly used for exploring the fine-grain state processor designs and evaluating their performance.

The out-of-order superscalar description of FAST lacked the cache simulator and assumed a perfect cache hierarchy system. As one of the contributions, this work implements a cache hierarchy simulation system written in ADL and integrates it into the FAST superscalar description and extends the previous simulators. This cache simulation

Figure 3.3. Superscalar Simulator

system supports multiple levels of caches, either blocking or non-blocking, from direct-mapped to n-way associativity. It also supports different replacement policies, including FIFO, LRU, and RANDOM. Moreover, it actually moves data from and to the CPU cores. Unlike the Dinero IV [15] cache simulator which was tried to be integrated with FAST, it can generate not only the hit and miss information but also the accurate latency information.

Shown in Listing 3.1, each level of the cache is defined as a *Cache Artifact*, allowing it easily to be integrated with different simulators.

## 3.2 Benchmark Suites and Environment

In this work, we use the SPEC CPU2000 V1.2 [49] benchmark programs to evaluate different Fine-grain State Processor designs. SPEC CPU2000 V1.2 benchmark suites were

released by SPEC in 2001, including two sub-suites, CINT2000 and CFP2000. CINT2000 is used to measure and compare the compute-intensive integer performance. It contains 12 applications (11 in C and 1 in C++). CFP2000 is used to measure and compare the compute-intensive floating-point performance. It contains 14 applications (6 in Fortran-77, 4 in Fortran-90 and 4 in C).

```

artifact L1_cache

attributes

(  size ,           # cache size in KB

bpl ,            # cache line size in bytes

assoc ,          # n-way associativity

repl_policy ,   # block replacement policy

num_ports ,     # number of cache ports

num_mshrs ,     # number of outstanding misses

hit_latency ,   # latency to access cache

bandwidth       # data bus bandwidth

)

begin

...

end

```

**Listing 3.1. Cache Artifact**

Our experimental hardware consists of a cluster of 20 machines with Intel(R) Xeon(R) CPUs, running the Linux OS. The SPEC CPU2000 benchmark programs are compiled with the GNU GCC cross compiler targeting the MIPS IV instruction set. Some of these benchmarks have not been simulated because of system libraries, e.g., Fortran 90 and C++ benchmarks. Therefore they have been excluded from our experiments. Nine integer programs and eight floating-point programs are used to analyze the FSP performance, which are shown in Listing 3.2 and Listing 3.3, respectively.

| Name        | Remarks                            |

|-------------|------------------------------------|

| 164.gzip    | Data compression utility           |

| 175.vpr     | FPGA circuit placement and routing |

| 176.gcc     | C compiler                         |

| 181.mcf     | Minimum cost network flow solver   |

| 186.crafty  | Chess program                      |

| 197.parser  | Natural language processing        |

| 253.perlbmk | Perl                               |

| 256.bzip2   | Data compression utility           |

| 300.twolf   | Place and route simulator          |

**Listing 3.2. CINT2000 Benchmarks**

| Name       | Remarks                                                                              |

|------------|--------------------------------------------------------------------------------------|

| 171.swim   | Shallow water modeling                                                               |

| 172.mgrid  | Multi-grid solver in 3D potential field                                              |

| 173.applu  | Parabolic/elliptic partial differential equations                                    |

| 177.mesa   | 3D Graphics library                                                                  |

| 179.art    | Neural network simulation; adaptive resonance theory                                 |

| 183.equake | Finite element simulation; earthquake modeling                                       |

| 188.ammp   | Computational chemistry                                                              |

| 301.apsi   | Solves problems regarding temperature, wind, velocity and distribution of pollutants |

**Listing 3.3. CFP2000 Benchmarks**

Another important consideration about the simulation is the simulation time. As it is well known, it is really time-consuming and resource-consuming to run an application through an execution-driven cycle-accurate superscalar processor simulator. It can easily take a couple of weeks to emulate a SPEC CPU2000 benchmark running with the default reference input. In this work, in order to evaluate and compare different FPS designs, we

need to run CPU benchmarks using different simulators with many different configurations. It will be impracticable to run them all to completion with the default reference inputs. We therefore choose to run SPEC CPU2000 benchmarks to completion with a *reduced input* [29].

When SPEC CPU95 benchmark suites were integrated into FAST, the reduced input scheme was already applied. Compared to the partial running schemes, it can achieve much more accurate analysis within a reasonable time. In this work, we apply the MinneSPEC [29] reduced workload to emulate SPEC CPU2000 benchmark suites in FAST. MinneSPEC has been officially recognized by SPEC and is distributed with Version 1.2 and higher of SPEC CPU2000 benchmark suites. Although some benchmarks produce very different behavior with the MinneSPEC workload, most match the default reference workload program behavior very closely, in terms of function-level execution patterns, instruction mixes, and memory behavior [29]. From our experiments, MinneSPEC works well in FAST and it satisfies our research requirements.

# Chapter 4

## Taxonomy of Fine-grain State Processors

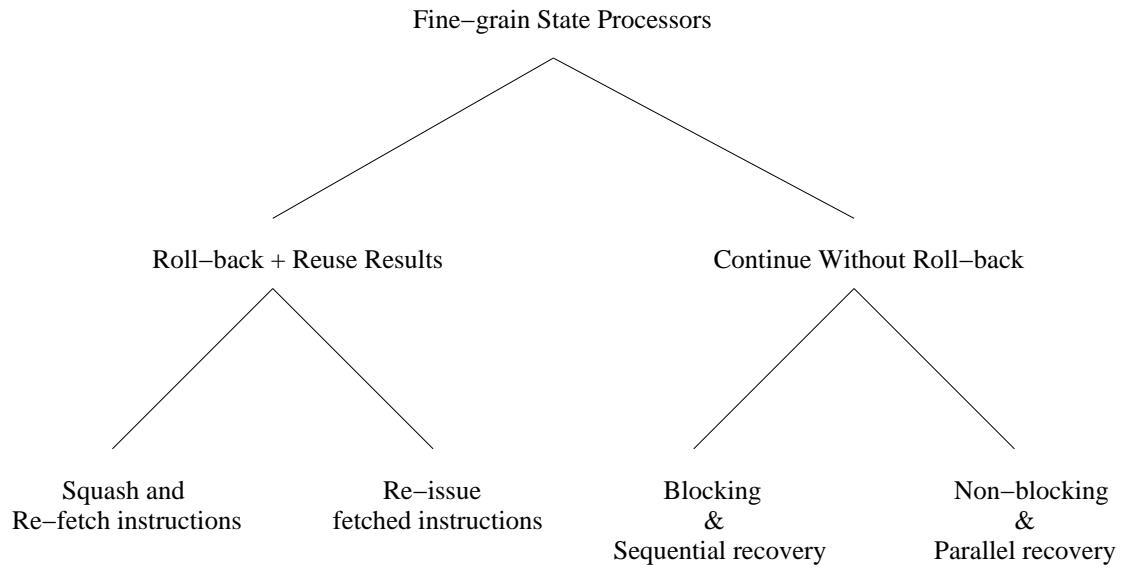

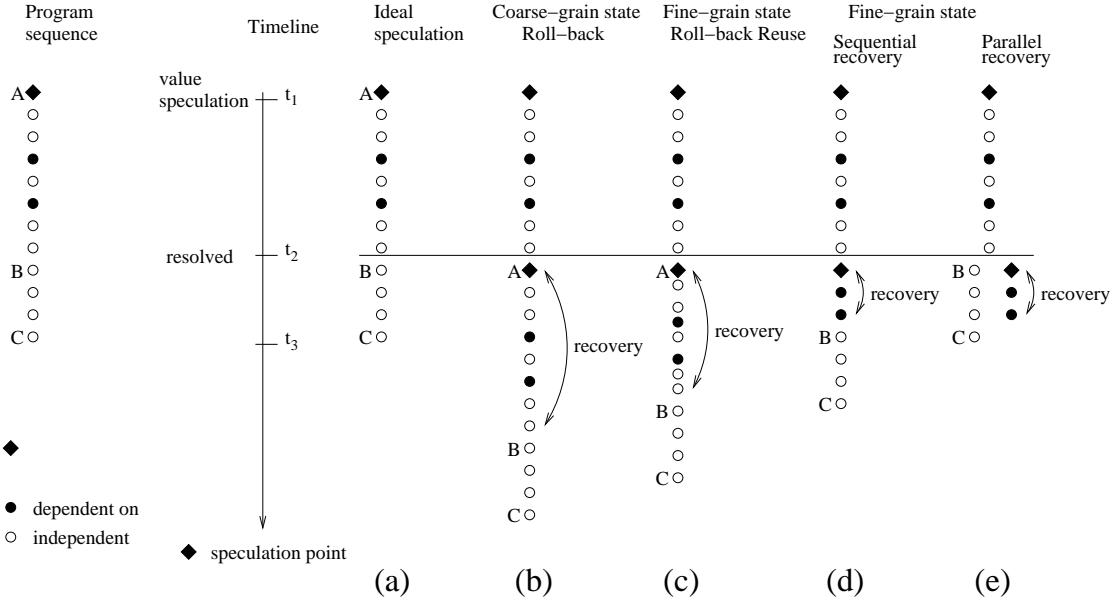

In this chapter, we introduce a taxonomy of the fine-grain state processors. It has two main categories, which can be divided further into four sub-categories, shown in Figure 4.1. Based on this taxonomy, those traditional proposals can be summarized and classified into the proper categories.

Figure 4.1. Taxonomy of Fine-grain State Processors

## 4.1 Roll-back + Reuse Results

The first main category is referred to as *Roll-back + Reuse Results*. Utilizing this technique, a processor is able to salvage part of finished work during the speculative execution after a missed speculation. When a mis-speculation happens, the processor rolls back from the exception point and restarts the execution. Those mis-speculation independent instructions may reuse previously generated results and skip different phases of execution (e.g., issue, execute, and result bypass). Thus, performance is improved. Furthermore, it can be divided into two sub-categories: *Squash and Re-fetch instructions* and *Re-issue fetched instructions*.

### 4.1.1 Squash and Re-fetch Instructions

Utilizing this technique, upon a mis-speculation, processor squashes all instructions following the mis-speculation point. It rolls back to the mis-speculation point and re-fetches all instructions. With the fine-grain state information, fetched instructions will reuse the buffered previous results if they are mis-speculation independent. The previously generated results are explicitly reused.

A typical application of this technique is the recovery of branch mis-predictions. The scenario of control independence gives the opportunity to reuse results based on the fine-grain state concept. A study of the control independence in superscalar processors [43] reported typical performance improvements of 10-30% when micro-architectural implementation issues are realistically modeled to exploit the control independence.

Several mechanisms have been proposed to reuse the results of control independent instructions.

Sodani and Sohi introduced the concept of dynamic instruction reuse in [48]. In their mechanism, the fine-grain state of previously executed instructions are buffered in the Reuse Buffer (RB), including the operands and destination results. Querying RB via the program counter, an instruction can reuse the result of the previous instance if the operands are the same. Their initial goal was to reduce the branch mis-prediction penalty by reusing control independent instructions. Interestingly, this concept can be extended to the general reuse.

Roth and Sohi proposed the register integration mechanism in [44] to reuse the results. Upon a mis-speculation, instructions after the mis-speculation point are squashed in the reverse order. Instead of recycling the allocated physical registers, register mappings of each instruction's operands and results are entered into the Integration Table (IT). Any new instruction will index IT using its PC to check if the register mappings of the operands match. If so, it can reuse the previous instance's destination physical register. Reusing is achieved through the register renaming, and no additional values are read from or written to the physical register file.

Chou *et al.* [10] presented the concept of dynamic control independence (DCI) to implement the reuse. A shadow copy of the Reorder Buffer, DCI buffer, is used to remember the state of recently fetched instruction. After a branch mis-prediction, all instructions following the mis-predicted branch are flushed from the ROB but they remain

in the DCI buffer. When a new instruction is fetched from the correct path, it associatively searches the DCI buffer. It can reuse its previous state stored in the DCI buffer if it proves to be control and data independent.

Besides the branch speculation, *Squash and Re-fetch instructions* is also utilized for other speculation mechanisms. Mutlu *et al.* [35] evaluated reusing the results of pre-executed instructions in a runahead execution processor. They reported that even an ideal reuse scheme can achieve only 3% improvement. The reason is the results of a small number of instructions pre-executed in runahead mode can be reused.

#### 4.1.2 Re-issue Fetched Instructions

Using the *Re-issue fetched instructions* technique, upon a mis-speculation, the processor still needs to roll back to the mis-speculation point and restart execution. However, it does not need to squash instructions and re-fetch instructions from the cache. The key point is that speculation dependent instructions are kept in the scheduling window even after they are issued. If the speculation is resolved as a miss, the processor can roll back to the mis-speculation point and re-issue only dependent instructions without re-fetching. On the other hand, since the independent instructions were already processed, their results can be implicitly reused.

A typical application of this technique is the recovery of load mis-speculations. When a load mis-speculation is detected, instead of squashing all instructions following the load and re-fetching instructions from the cache, the processor will re-issue instructions dependent on the mis-speculated load. In [20], Pentium 4 processor schedules instructions

dependent on loads assuming that loads would hit in the L1 data cache. If a load misses, a selective recovery mechanism called *replay* is used to wake up and re-issue dependent instructions previously executed using incorrect data.

Gandhi *et al.* [16] utilized this technique and proposed Selective Branch Recovery (SBR) to reuse results of convergence instructions. SBR exploits a frequently occurring type of control independence, called exact convergence, where the mis-predicted path converges exactly at the beginning of the correct path. Thus, upon a mis-prediction, correct instructions from the correct path are in fact already in the pipeline. In this case, the processor can reuse results of data independent convergent instructions and re-issue convergent false data dependent instructions without having to fetch/ rename them again.

## 4.2 Continue Without Roll-back

The second main category of the fine-grain state guided speculation recovery technique, *Continue Without Roll-back*, utilizes the fine-grain state concept more efficiently than *Roll-back + Reuse Results*. It is able to continue execution without rolling back to the mis-speculation point. It can also be divided into two sub-categories: *Sequential recovery* and *Parallel Recovery*.

### 4.2.1 Sequential Recovery

With the *Sequential recovery* scheme, the processor stops moving forward when a speculation is resolved as a miss. The miss dependent instructions, which should have been already buffered on on-chip structures, *e.g.*, *slicing buffer*, are re-executed to repair the

state. Once recovery is processed, the processor achieves a correct state at the resolution point and it can move forward.

Sarangi *et al.* [45] applied this technique in the context of Thread-Level Speculation (TLS) and proposed a novel architecture, *ReSlice*. If a value mis-prediction is declared, only the speculatively-retired instructions depended on the mis-predicted value, *Forward Slice*, are re-executed to restore the damaged state. Once the damaged state is repaired and merged into the processor state, processor is able to resume execution at the mis-speculation resolution point.

The *Sequential recovery* technique is also applied in the context of data cache miss speculation. In [51], Srinivasan *et al.* proposed the continual flow pipelines (CFP) model. Once a load instruction misses in the L2 data cache, the miss-dependent instructions (slices) are drained out of the pipeline into a slice buffer. In the meantime, CFP executes independent instructions. After the L2-miss is serviced, new front-end instructions wait until the slice instructions are inserted back into the pipeline to construct the correct state.

#### 4.2.2 Parallel Recovery

Although the *Sequential recovery* scheme is an efficient fine-grain state based technique, it does not fully exploit the power of the fine-grain state concept. That is, at the mis-speculation resolution point, the execution is blocked needlessly until the recovery is done. Because of the blocking, the parallelism available during the recovery is not exploited. Since an FSP is aware of the state at the individual basis, it can continue processing seamlessly with a partially correct state, before the whole state is repaired. In parallel

with the recovery, the processor can move forward and execute new instructions.